过去十年是深度学习的“黄金十年”,它彻底改变了人类的工作和娱乐方式,并且广泛应用到医疗、教育、产品设计等各行各业,而这一切离不开计算硬件的进步,特别是GPU的革新。

深度学习技术的成功实现取决于三大要素:第一是算法。20世纪80年代甚至更早就提出了大多数深度学习算法如深度神经网络、卷积神经网络、反向传播算法和随机梯度下降等。

第二是数据集。训练神经网络的数据集必须足够大,才能使神经网络的性能优于其他技术。直至21世纪初,诸如Pascal和ImageNet等大数据集才得以现世。 第三是硬件。只有硬件发展成熟,才能将大型数据集训练大型神经网络的所需时间控制在合理的范围内。业内普遍认为:比较“合理”的训练时间大概是两周。

至此,深度学习领域燃起了燎原之火。 如果把算法和数据集看作是深度学习的混合燃料,那么GPU就是点燃它们的火花,当强大的GPU可用来训练网络时,深度学习技术才变得实用。

此后,深度学习取代了其他算法,被广泛应用在图像分类、图像检测、语音识别、自然语言处理、时序分析等领域,甚至在围棋和国际象棋方面也能看到它的身影。随着深度学习潜入人类生活的方方面面,模型训练和推理对硬件的要求也越来越高。

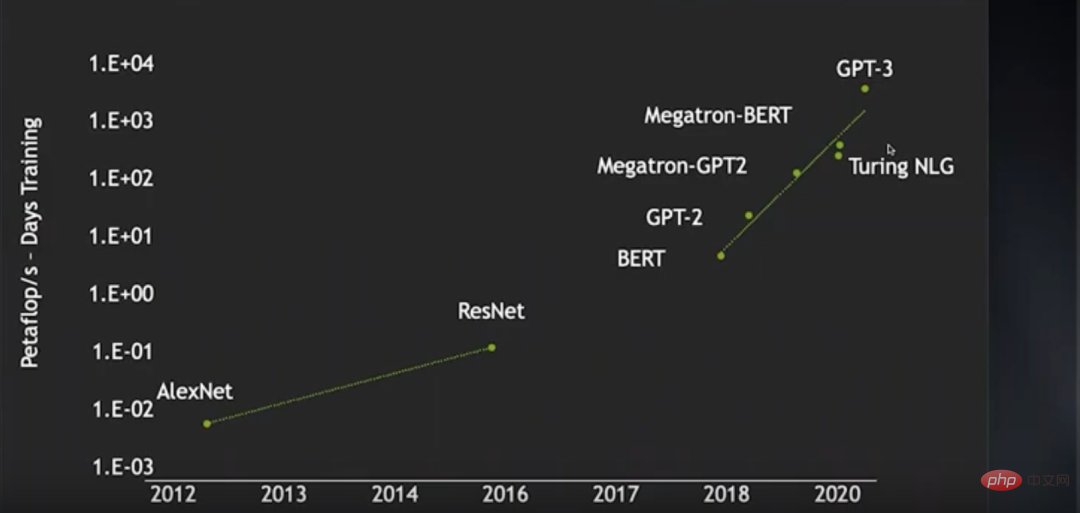

从2012年AlexNet出现到2016年ResNet问世,图像神经网络的训练算力消耗(以petaflop/s-day为单位)增长了将近2个数量级,而从2018年的BERT到近年的GPT-3,训练算力消耗增加了近4个数量级。在此期间,得益于某些技术的进步,神经网络的训练效率明显提升,由此节省了不少算力,否则算力消耗的增长还会更夸张。

研究人员想用更大的无监督语言数据集训练更大的语言模型,然而,尽管他们已经拥有4000个节点的GPU集群,但在合理训练时间内能处理的运算还是非常有限。这就意味着,深度学习技术的发展有多快,取决于硬件发展有多快。

如今,深度学习模型不但越来越复杂,而且应用范围越来越广泛。因此,还需要持续提升深度学习的性能。 那么,深度学习硬件究竟如何继续提升?英伟达首席科学家Bill Dally无疑是回答这一问题的权威,在H100 GPU发布前,他在一次演讲中回顾了深度学习硬件的现状,并探讨摩尔定律失效的情况下持续提升性能扩展的若干方向。OneFlow社区对此进行了编译。

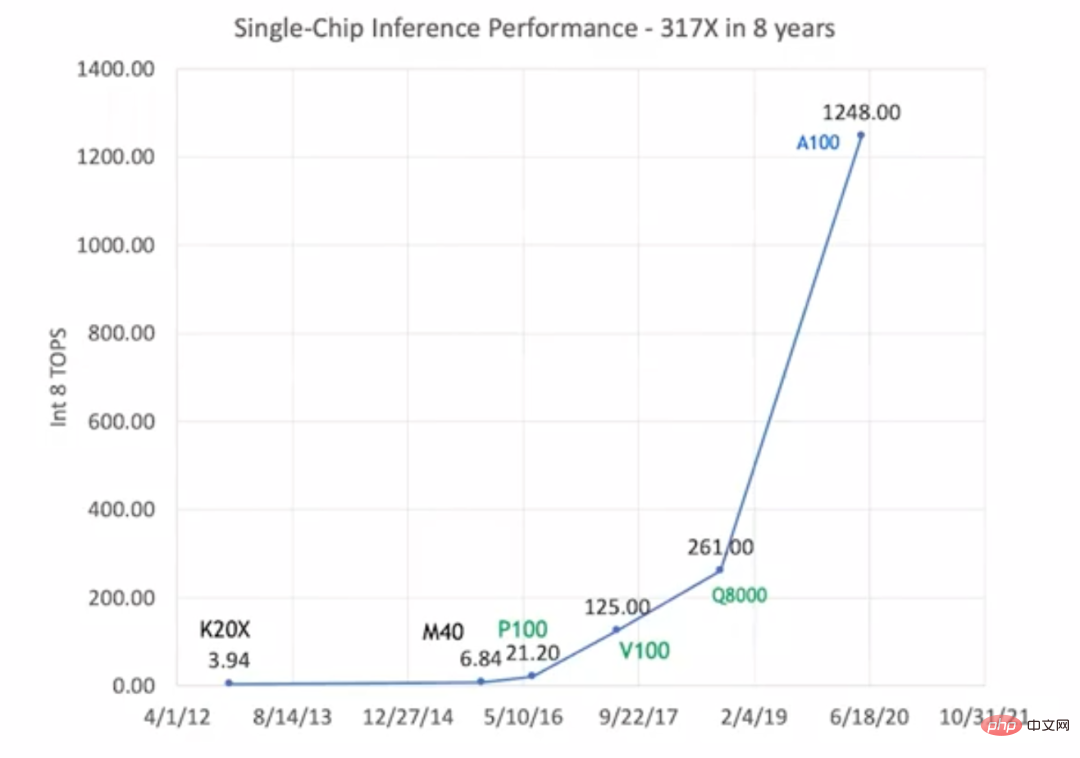

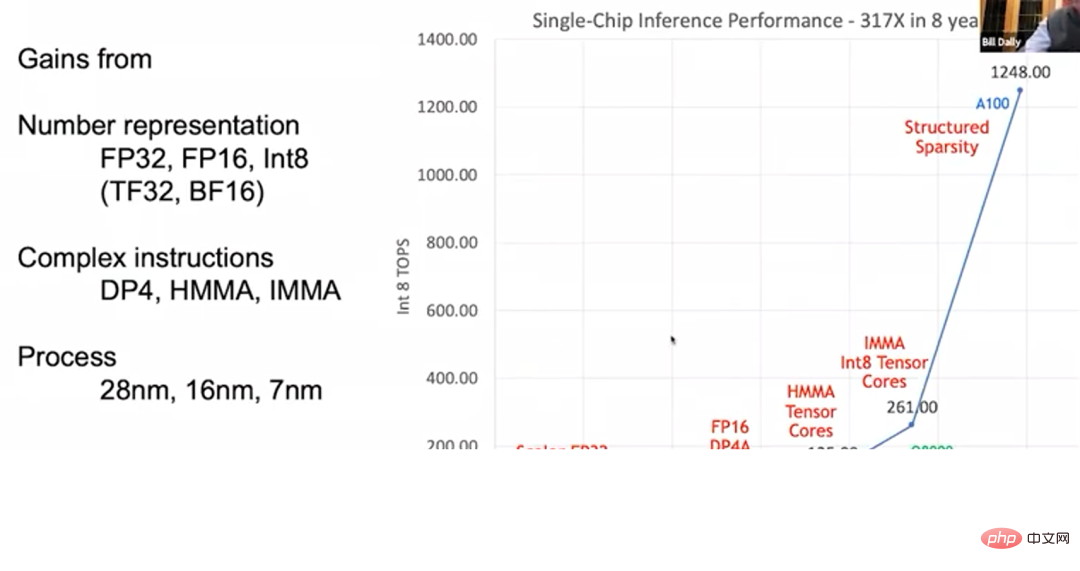

从2012年的K20X到2020年的A100,GPU的推理性能提高到原来的317倍。这就是我们所说的“黄氏定律”,这种发展速度比“摩尔定律”快得多。

GPU的推理性能提升但不同于“摩尔定律”,在“黄氏定律”中,GPU的性能提升不完全依赖制程技术的进步。上图用黑、绿、蓝三色分别标注了这几种GPU,分别代表它们使用了三种不同的制程技术。早期的K20X和M40使用的是28纳米制程;P100、V100和Q8000使用的是16纳米制程;A100使用的是7纳米制程。制程技术的进步大概只能让GPU的性能提高到原来的1.5或2倍。而总体317倍的性能提升绝大部分归功于GPU架构和线路设计的完善。

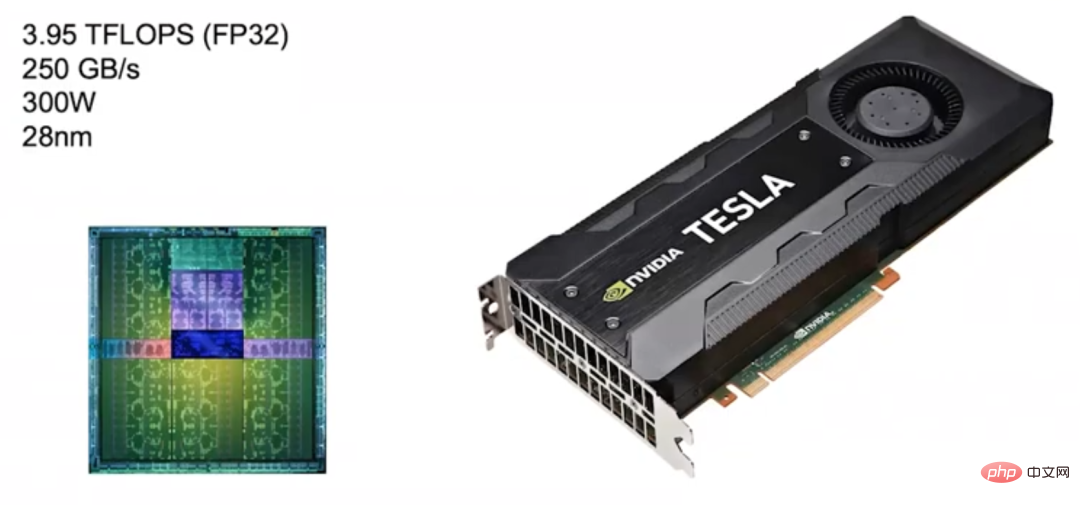

2012年,英伟达推出了一款Kepler架构GPU,但它并不是专为深度学习设计的。英伟达在2010年才开始接触深度学习,当时还没有考虑为深度学习量身定制GPU产品。

Kepler (2012)Kepler的目标使用场景是图像处理和高性能运算,但主要还是用于图像处理。因此,它的特点是高浮点运算能力,它的FP32计算(单精度浮点数计算)速度达到近4 TFLOPS,内存带宽达到250 GB/s。基于Kepler出色的性能表现,英伟达也将它视为自家产品的基准线。

Pascal (2016)后来,英伟达在2016年推出了Pascal架构,它的设计更适合深度学习。英伟达经过一些研究后发现,不少神经网络都可以用FP16(半精度浮点数计算)训练,因此Pascal架构的大部分型号都支持FP16计算。

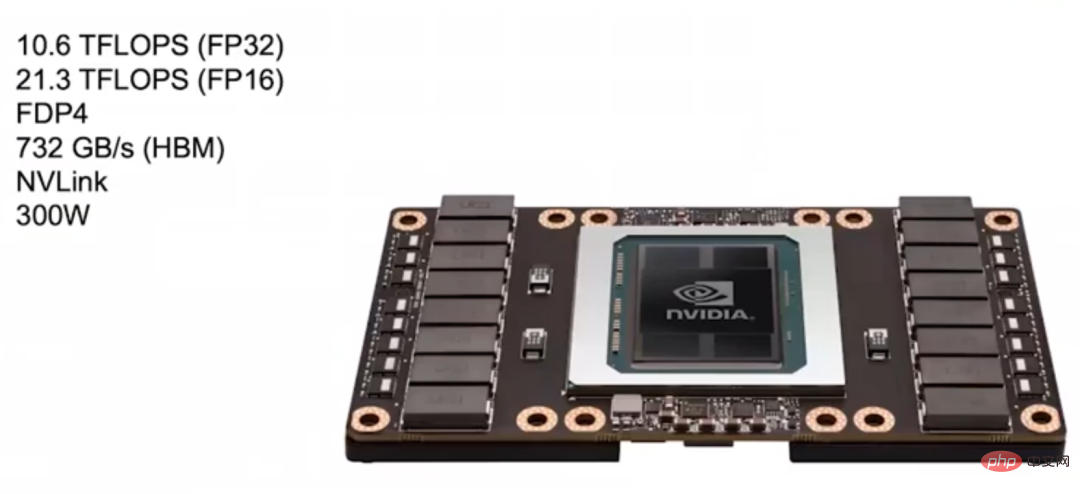

下图这款Pascal GPU的FP32计算速度可达10.6 TFLOPS,比前一款Kepler GPU高出不少,而它的FP16计算则更快,速度是FP32的两倍。

Pascal架构还支持更多复杂指令,例如FDP4,这样就可以将获取指令、解码和获取操作数的开销分摊到8个算术运算中。相较于之前的融合乘加(Fuse Multiply-Add)指令只能将开销分摊到2个算术运算,Pascal架构可以减少额外开销带来的能耗,转而将其用于数学运算。

Pascal架构还使用了HBM显存,带宽达到732 GB/s,是Kepler的3倍。之所以增加带宽,是因为内存带宽是深度学习性能提升的主要瓶颈。此外,Pascal使用了NVLink,可以连接更多机器和GPU集群,从而更好地完成大规模训练。

英伟达为深度学习推出的DGX-1系统就使用了8个基于Pascal架构的GPU。

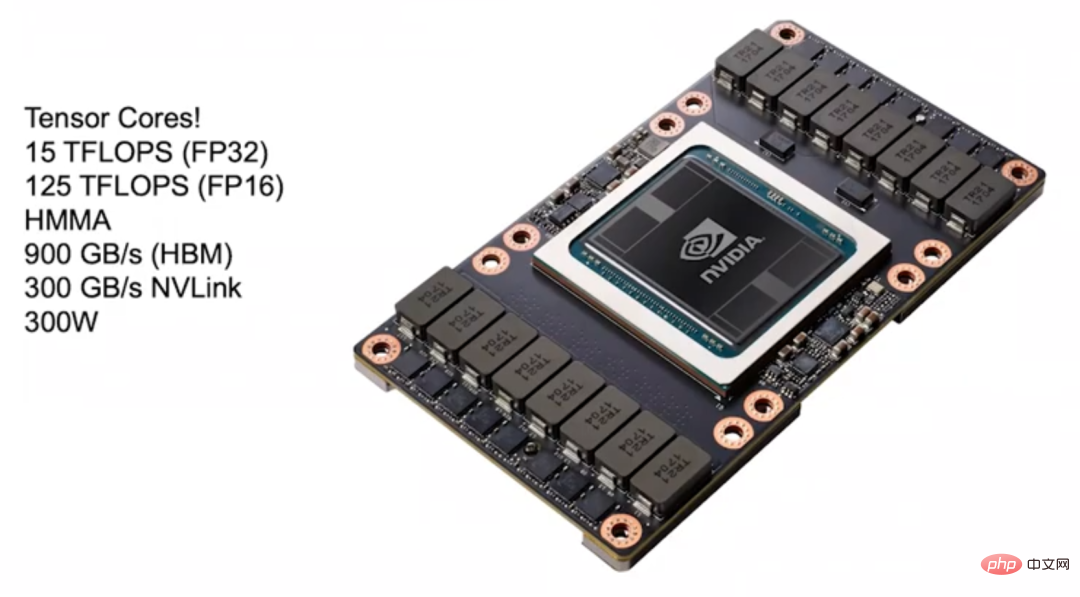

Volta (2017)2017年,英伟达推出了适用于深度学习的Volta架构,它的设计重点之一是可以更好地分摊指令开销。Volta架构中引入了Tensor Core,用于深度学习的加速。Tensor Core可以用指令的形式与GPU连接,其中的关键指令是HMMA (Half Precision Matrix Multiply Accumulate,半精度矩阵乘积累加),它将2个4×4 FP16矩阵相乘,然后将结果加和到一个FP32矩阵中,这种运算在深度学习中很常见。通过HMMA指令,就可以将获取指令和解码的开销通过分摊降低到原来的10%到20%。

剩下的就是负载问题。如果想要超越Tensor Core的性能,那就应该在负载上下功夫。在Volta架构中,大量的能耗和空间都被用于深度学习加速,所以即使牺牲可编程性,也不能带来太多性能提升。

Volta还升级了HBM显存,内存带宽达到900 GB/s,还使用了新版本的NVLink,可以让构建集群时的带宽增加到2倍。此外,Volta架构还引进了NVSwitch,可以连接多个GPU,理论上NVSwitch最多可以连接1024个GPU,构建一个大型共享内存机器。

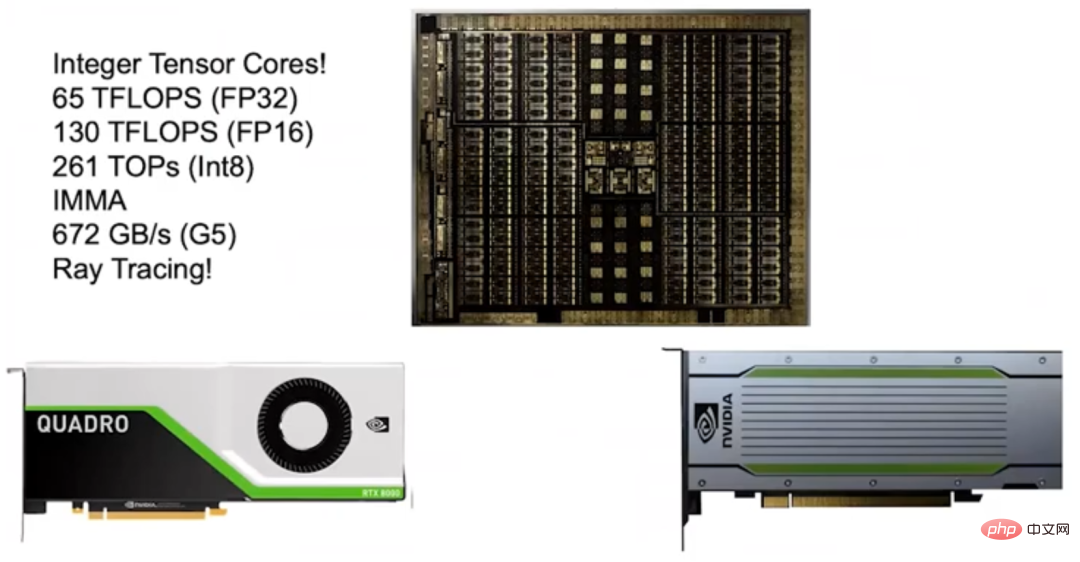

Turing (2018)2018年,英伟达推出了Turing架构。由于之前的Tensor Core大获成功,所以英伟达又顺势推出了Integer Tensor Core。因为大部分的神经网络用FP16即可训练,做推理时也不需要太高的精度和太大的动态范围,用Int8即可。所以,英伟达在Turing架构中引进了Integer Tensor Core,使性能提高到原来的2倍。

Turing架构还使用了GDDR显存,以支持那些有高带宽需求的NLP模型和推荐系统。当时有人质疑称,Turing架构的能源效率比不上市面上的其他加速器。但如果仔细计算,会发现其实Turing架构的能源效率更高,因为Turing用的是G5显存,而其他加速器用的是LPDDR内存。我认为,选择G5显存是一个正确的决定,因为它可以支持同类产品没能支持的高带宽需求的模型。

我对Turing架构深感骄傲的一点是,它还配备了支持光线追踪(Ray Tracing)的RT Core。英伟达在2013年才开始研究RT Core,在短短5年后就正式推出了RT Core。

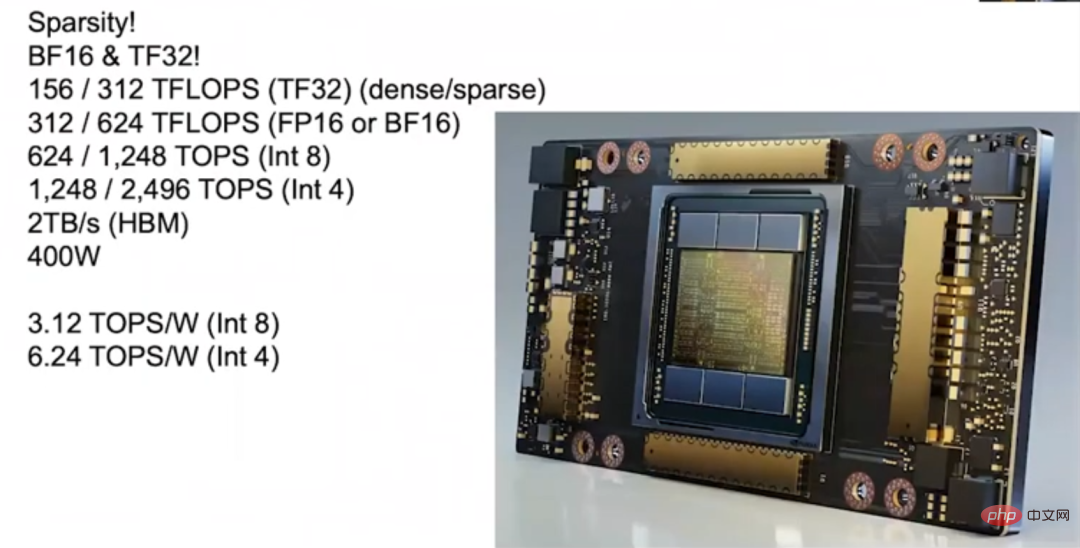

Ampere (2020)2020年,英伟达发布了Ampere架构,让当年发布的A100实现了性能飞跃,推理速度可达1200 Teraflops以上。Ampere架构的一大优点是,它支持稀疏性。我们发现,大部分神经网络都是可以稀疏化的,也就是说,可以对神经网络进行“剪枝”,将大量权重设置为0而不影响它的准确率。但不同神经网络的可稀疏化程度不同,这就有些棘手。比如,在保证不损失准确率的前提下,卷积神经网络的密度可以降低至30%到40%,而全连接神经网络则可降低至10%到20%。

传统观点认为,由于运算稀疏矩阵包的开销较大,所以如果密度不能降到10%以下,权衡之下不如运算密集矩阵包。我们一开始和斯坦福大学合作研究稀疏性,后来做出了很好的机器,它们在矩阵密度达到50%时也能高效运行,但要想让稀疏矩阵在电源门控(power gating)方面比密集矩阵更优越还是很困难,这是我们一直想突破的地方。

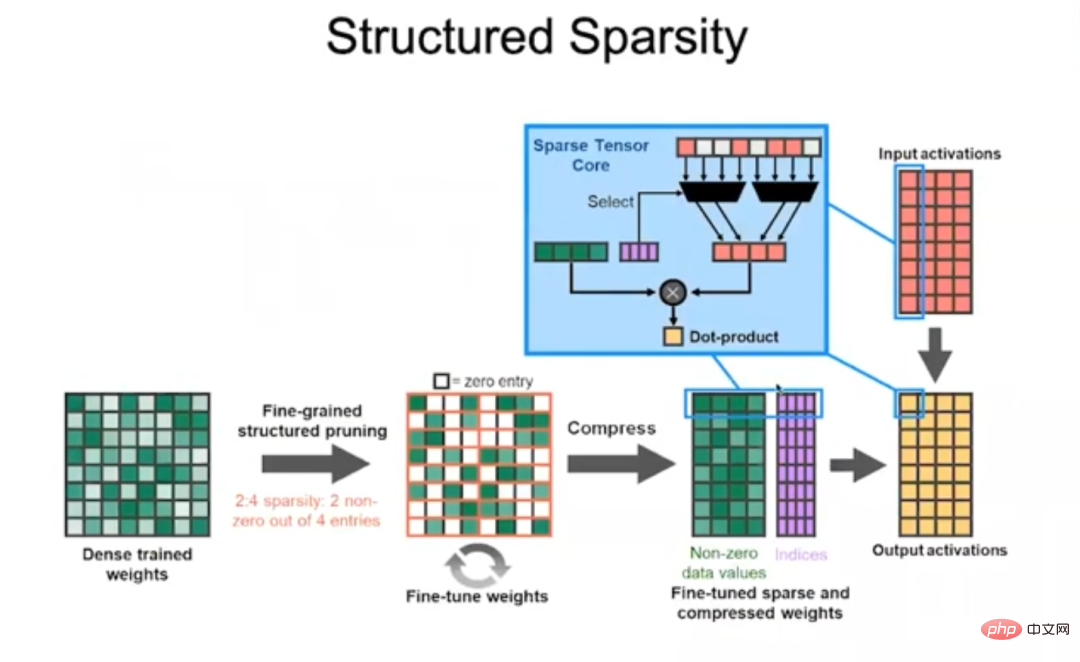

最终,我们攻破难题研发出了Ampere,而秘诀就是结构化稀疏。

结构化稀疏Ampere架构规定矩阵的每4个数值中,非零值不能超过2个,也就是通过去掉非零值对权重进行压缩。通过输入码字(code word)判断哪些权重应被保留,并用码字判断这些非零权重应该乘以哪些输入激活,然后相加,完成点乘操作。这种做法非常高效,让Ampere架构在大多数神经网络上的性能提升到原来的2倍。

此外,Ampere架构还有不少创新点,例如Ampere内置了TF32(即TensorFloat-32)格式,它结合了FP32的8位指数位和FP16的10位尾数位。Ampere还支持BFLOAT格式,BFLOAT的指数位与FP32相同,尾数位比FP32少,所以可以视为FP32的缩减版。上述的所有数据格式都支持结构化稀疏,所以无论用FP16和TF32训练,还是用Int8和Int4推理,都可以获得结构化稀疏带来的高性能。

随着Ampere在量化方面做得越来越好,它可以应用在很多神经网络上并保证高性能。Ampere有6个HBM堆栈,且HBM显存的带宽也有所升级,达到2TB/s。端到端推理时,Ampere的运算能力可达3.12 TOPS/W(Int8)和6.24 TOPS/W(Int4)。

GPU推理性能提升的三大因素总结深度学习过去的发展,GPU推理性能在8年内提升317倍主要归功于三大因素:

首先,最重要的是数字表示(number representation)法的发展。

FP32的精度太高,导致算术运算的成本太高。后来Turing和Ampere架构支持Int8,极大提升了GPU的每瓦性能。Google发表论文公布TPU1时表示,TPU1的优势就在于它是专门为机器学习量身定制的。实际上,Google应该是在拿自家的TPU1和英伟达的Kepler进行比较(如前所述,Kepler并非专门为深度学习而设计),所以TPU1的优势归根结底可以说是Int8相较于FP32的优势。

其次,GPU支持复杂指令。

Pascal架构新增了点乘指令,然后Volta、Turing和Ampere架构新增了矩阵乘积指令,让开销得到分摊。在GPU中保留可编程引擎可以带来很多好处,它可以像加速器一样高效,因为每项指令完成的任务非常多,每项指令的开销分摊几乎可以忽略不计。

最后,制程技术的进步。

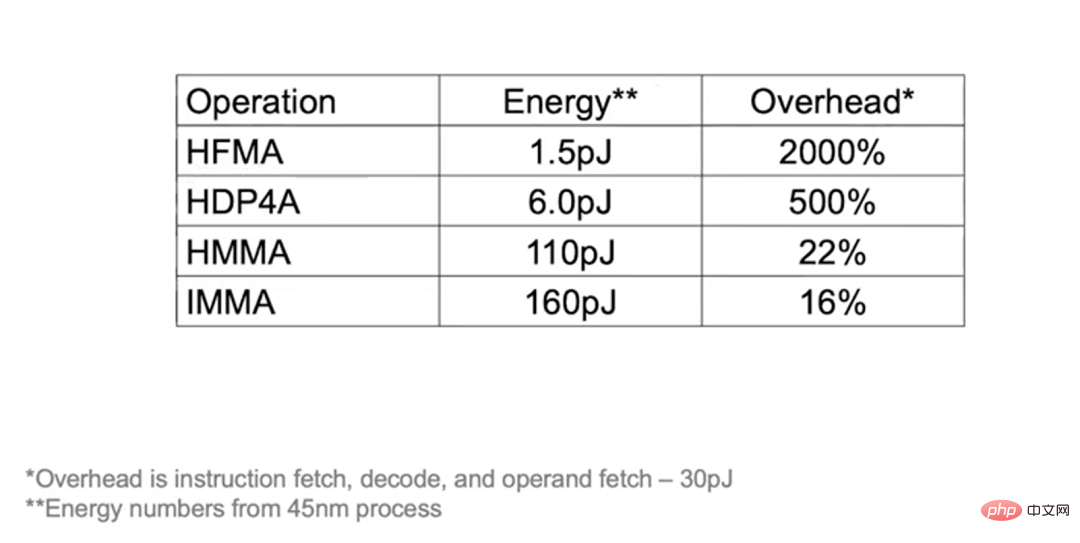

芯片制程从28纳米发展到如今的7纳米,为GPU性能提升作出了一定的贡献。 下列例子可以让你更好地理解开销分摊的效果:如果执行HFMA操作,“乘”和“加”2个操作合计只需1.5pJ(皮焦耳,Picojoules),然而获取指令、解码和获取操作数需要30pJ的开销,分摊下来开销就会高达2000%。

而如果执行HDP4A操作,就可以将开销分摊到8个操作,使开销下降至500%。而HMMA操作,由于绝大部分的能耗都用于负载,开销仅为22%,IMMA则更低,为16%。因此,虽然追求可编程性会增加少量开销,但采取不同的设计可带来的性能提升更加重要。

以上谈论的都是单个GPU的性能,但训练大型语言模型显然需要多个GPU,因此还要改善GPU之间的连接方式。 我们在Pascal架构中引入NVLink,后来的Volta架构采用了NVLink 2,Ampere架构采用了NVLink 3,每一代架构的带宽都翻了一倍。此外,我们在Volta架构中推出了第一代NVSwitch,又在Ampere架构推出了第二代。通过NVLink和NVSwitch,可以构建超大型的GPU集群。另外,我们还推出了DGX box。

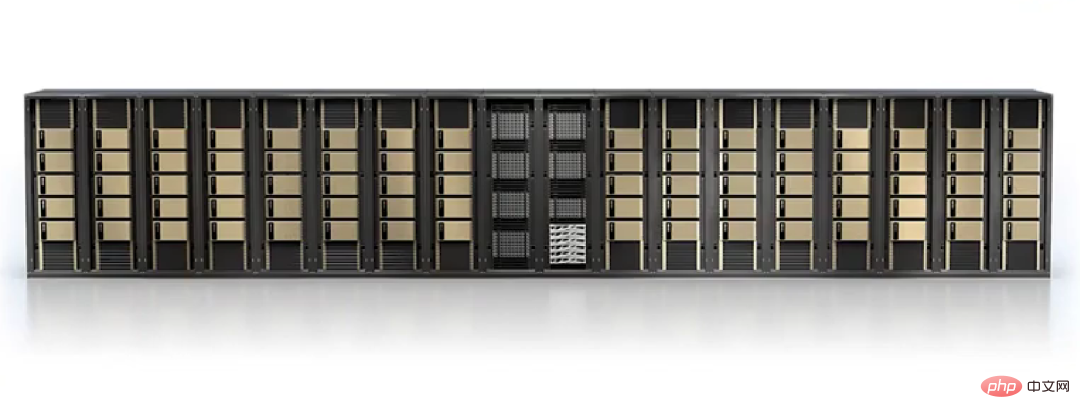

DGX box

2020年,英伟达收购了Mellanox,所以现在可以提供包含Switches和Interconnect在内的整套数据中心解决方案,供构建大型GPU集群之用。此外,我们还配备了DGX SuperPOD,它在AI性能记录500强名单上排行前20。以往,用户需要定制机器,现在只需要购置一台可以部署DGX SuperPOD的预配置机器,就可以获得DGX SuperPOD带来的高性能。此外,这些机器还非常适用于科学计算。

从前,用单台机器训练单个大型语言模型需要几个月之久,但通过构建GPU集群就可以大大提高训练效率,因此,优化GPU集群连接和提升单个GPU的性能同样重要。

接下来谈谈英伟达的加速器研发工作。英伟达把加速器视为试验新技术的载体,成功的技术最终会被应用到主流GPU中。 可以这样理解加速器:它有一个由内存层次结构输入的矩阵乘法单元,接下来要做的是让大部分的能耗用于矩阵乘法计算,而不是用于数据搬运。

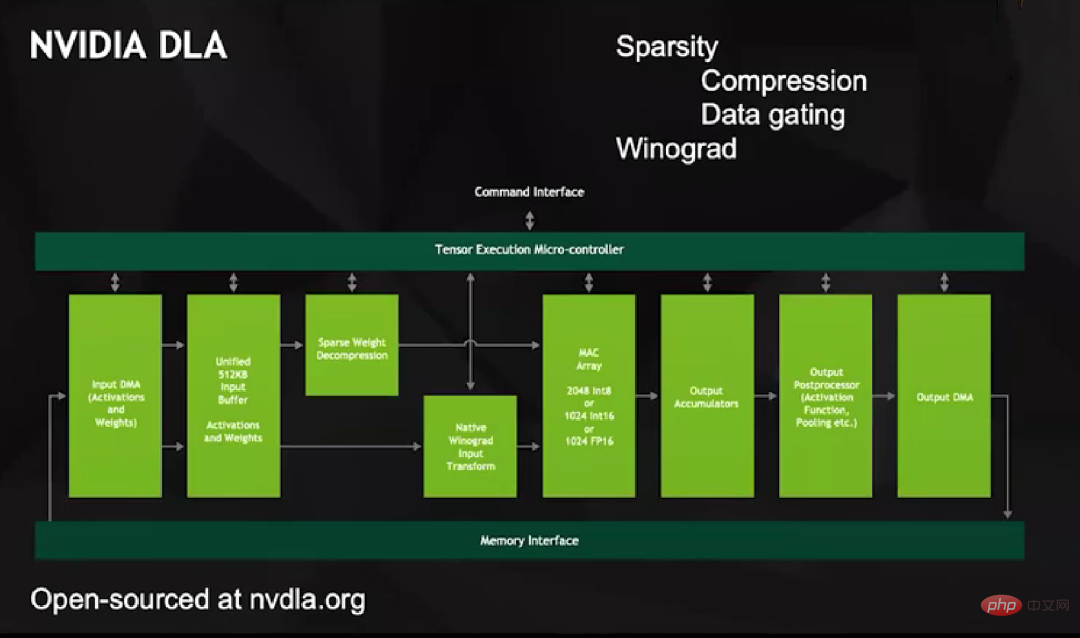

为了这个目标,我们在2013左右启动了NVIDIA DLA项目,它是一款开源产品,配套非常完善,与其他深度学习加速器别无二致。但DLA有大型MAC阵列,支持2048次Int8、1024次Int16或1024次FP16操作。

DLA有两个独特之处:一是支持稀疏化。我们从容易实现的目标开始着手,所有的数据传输,包括从DMA到Unified Buffer和从Unified Buffer到MAC阵列,都只涉及非零值,通过编码决定哪些元素被留下,然后对这些元素进行解压缩,再输入MAC阵列进行运算。

DLA解压缩的方式比较巧妙,它并不向MAC阵列中输入零值,因为这会让一连串的数据都变为零。相反,它设置了单独的线路表示零值,当乘法器在任一输入中接收到该线路时,就会锁定乘法器内的数据,然后发送输出,输出的数据不会增加任何数值,这种数据门控(Data Gating)的能源效率非常高。

二是在硬件层面支持Winograd变换。要知道,如果要做卷积,例如一个m×n的卷积核,在空间域就需要n的2次方个乘法器和加法器,但如果在频域,就只需要逐点相乘。 所以大型卷积核在频域运算比在空间域运算更高效。根据卷积核大小的不同,对部分图像网络而言,Winograd变换可以带来4倍的性能提升。

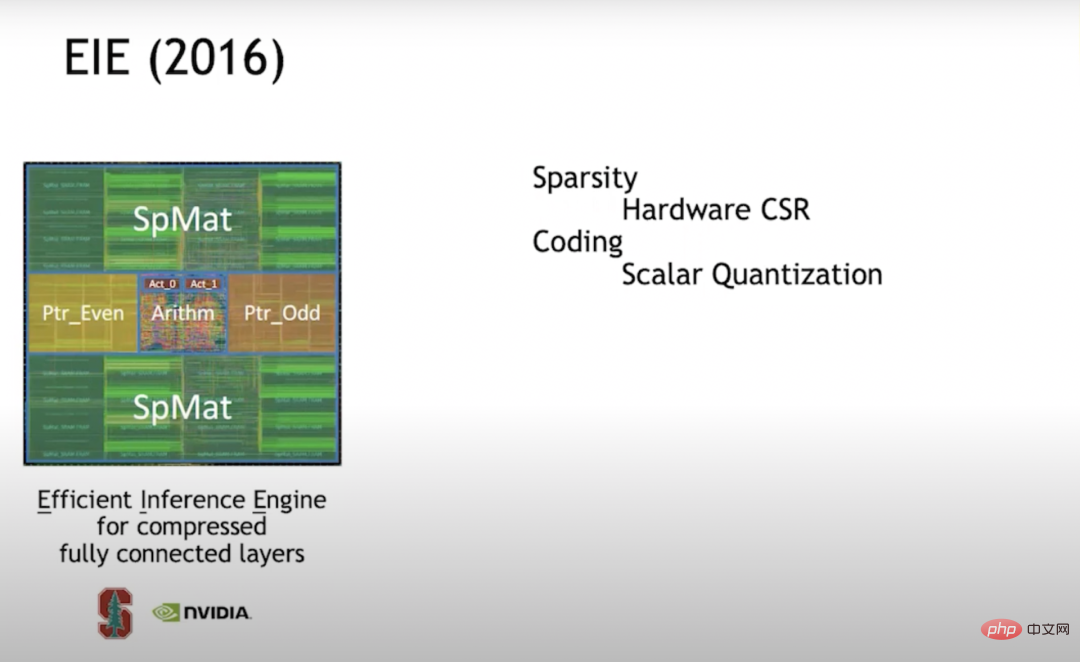

EIE(2016)2016年,我在斯坦福和我当时的学生韩松(MIT EECS助理教授、原深鉴科技联合创始人)一起研究EIE (Efficient Inference Engine)。这是对稀疏化的初步探索之一。我们在硬件层面支持CSR(Compressed Sparse Row)矩阵表示,这种做法非常高效,在密度为50%时,甚至比全密度计算还要节能。

后来发现,如果想让加速器更高效,应该构建向量单元阵列,这样每个引擎不会只执行单个乘加,而是每个循环每个PE(Processing Element)执行16×16=256个乘加。但当我们开始构建向量单元阵列时,发现很难高效实现稀疏化,于是转而采用结构化稀疏。

EIE处理标量单元时,它将指针结构储存在单独的内存中,然后通过流水阶段来处理指针结构,决定哪些数据可以相乘,继而执行乘法,将运算结果放置在合适的位置。这一整套流程运行得非常高效。 我们还发现,提高神经网络运算效率的方法除了“剪枝”实现稀疏化之外,还有量化。因此,我们决定使用码本量化(codebook quantization)。在用比特数表示的数据方面,码本量化是提升效率的最佳方法。所以我们对codebook(码本)进行了训练。

事实证明,如果你能使用反向传播来捕捉梯度下降,那就可以将反向传播运用到任何事物中。所以我们在码本中使用反向传播,训练了给定精度的最优码字集。假设码本有7个比特,那么你将得到128个码字,我们就在神经网络中找到最优的128个码字进行训练。

码本量化面临一个问题:数学运算的开销很高。因为不管码本有多大,实际数值是多少,你都需要在RAM(随机访问内存)中进行查找。实际数值必须以高精度表示,而你无法将这些码字准确地表示出来。 因此,我们在高精度数学方面花了很多精力。从压缩的角度来看,这样做的效果很好,但从数学能量(math energy)的角度来看,就显得不是很划算,所以在后续工作中我们就放弃了这项技术。

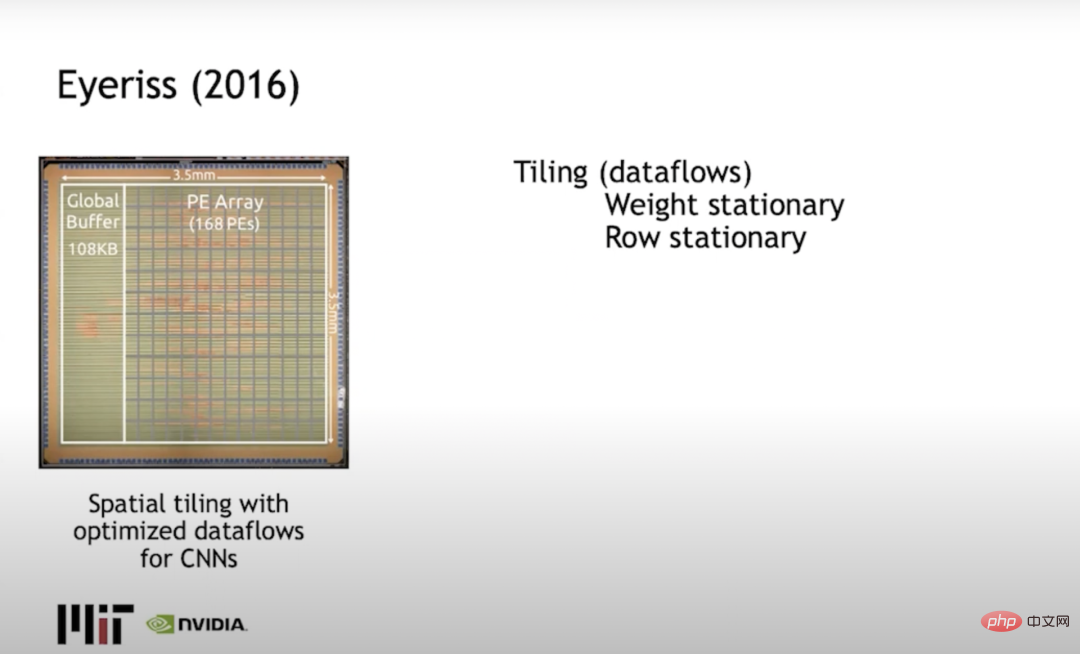

Eyeriss(2016)Joel Emer(同时供职于英伟达和麻省理工大学)和麻省理工大学的Vivienne Sze一起构建了Eyeriss,主要解决了平铺问题,或者说是如何限制计算,以此来将数据搬运(data movement)最小化。典型的方法是使用行固定(row stationary),在行中传播权重,输出在列中激活,并最大限度地减少数据搬运消耗的能量。

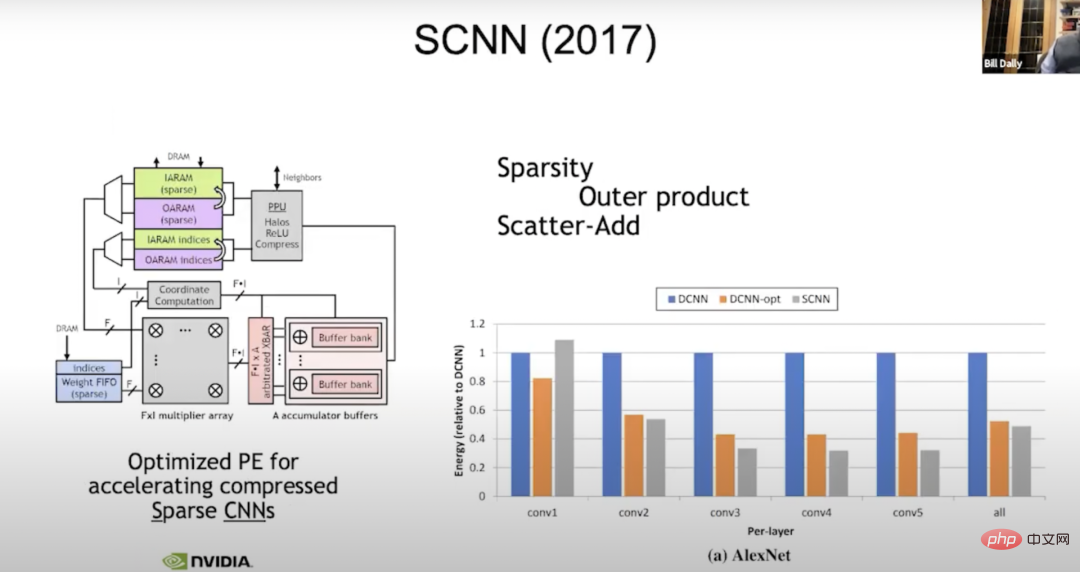

SCNN(2017)我们现在仍在进行稀疏性研究。2017年,我们为稀疏编译(神经网络的进化版)搭建了一台名为SCNN(Sparse CNNs)的机器,我们所做的是:将与处理稀疏性相关的所有复杂问题都转移到输出上。读取所有的输入激活,同时明确它们需要去往哪里,因此这里的“f宽向量”是典型的向量输入激活。

我们一次会读取四个输入激活,四个权重,每个权重都需要乘以每个输入激活。这只是一个关于把结果放在哪里的问题,所以我们用f乘f计算。

在坐标计算中,我们取输入激活和权重的指数,并计算出在输出激活中需要求和结果的位置。然后在这些累加器缓冲区上做了一个数据发散(scatter_add)计算。在此之前,一切都非常有效。但事实证明,将不规则性转移到输出上不是一个好办法,因为在输出中,精度实际上是最宽泛的。当你倾向于累加,做了八位权重,八位激活,累加到了24位。在这里我们用宽位累加器(wide accumulators )做了大量的数据搬运,效果优于做更密集一点的数据搬运。不过提升也没有想象的那么多,也许是密度单元能量的50%。

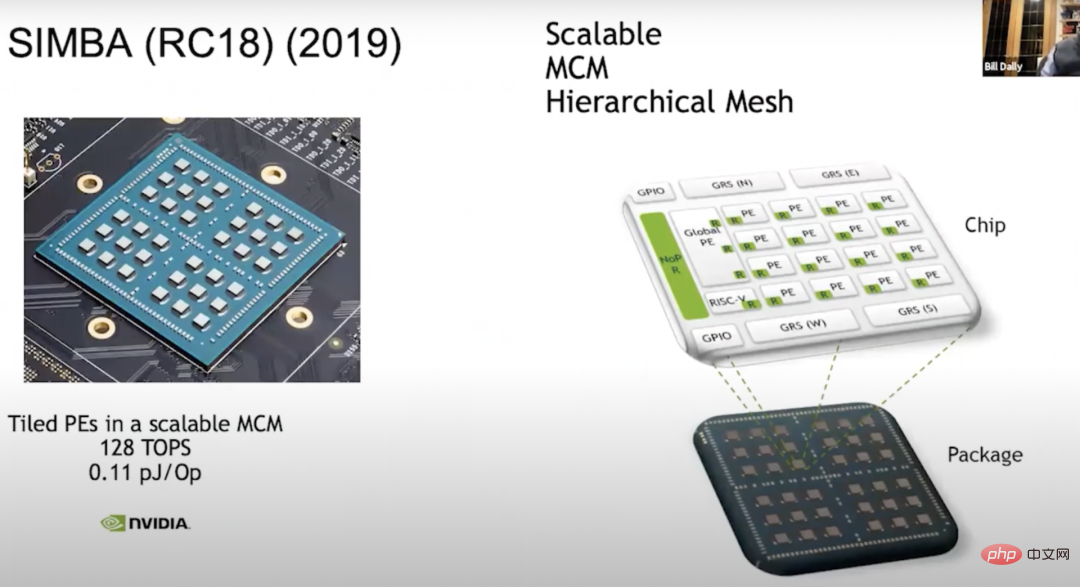

SIMBA(RC18)(2019)我们要做的另一件事是:用现有加速器建造一个多芯片模块——SIMBA(RC18),在2018年产生了做此研究的想法,同时这款芯片也展示了很多巧妙的技术。它有一个很好的PE架构,该芯片则在其中间提供了一项非常有效的信令技术(signaling technology)。现在该架构扩展到了完整的36个芯片,其中每个芯片都有一个4x4的PE矩阵,在这个单位中,每个PE又有8个宽矢量单位,因此我们能够得到128 TOPS的运算能力,每个Op有0.1 pJ,大约相当于10 TOPS/W。

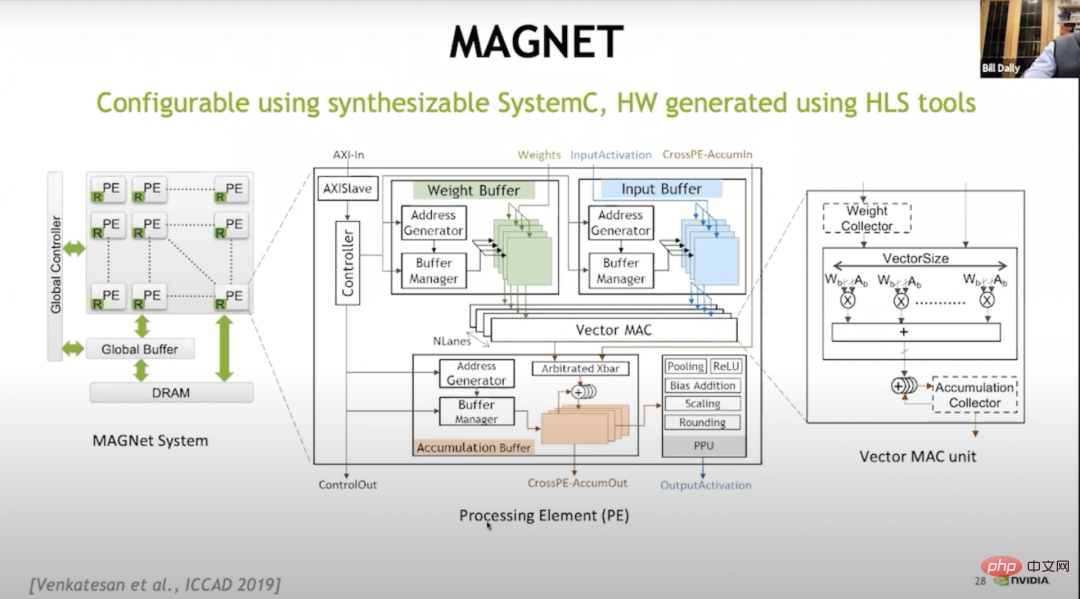

从中我们学到了很多关于权衡(trade-offs)的东西。 我们意识到:构建这些PE阵列宛如建立一个非常大的设计空间(design space),关乎如何构建内存层次结构,如何调度数据等等,对此我们建立了一个叫做MAGNET的系统。

MAGNET上图是一个于2019年发表在ICCAD(国际计算机辅助设计会议)上的设计空间探索系统,主要用于枚举其设计空间,如:每个向量单元应该有多宽,每个PE有多少向量单元,权重缓冲区有多大,累加器缓冲区有多大,激活缓冲区有多大等等。后来发现,我们需要去做另一个级别的缓存,于是添加了权重收集器和累加器收集器。

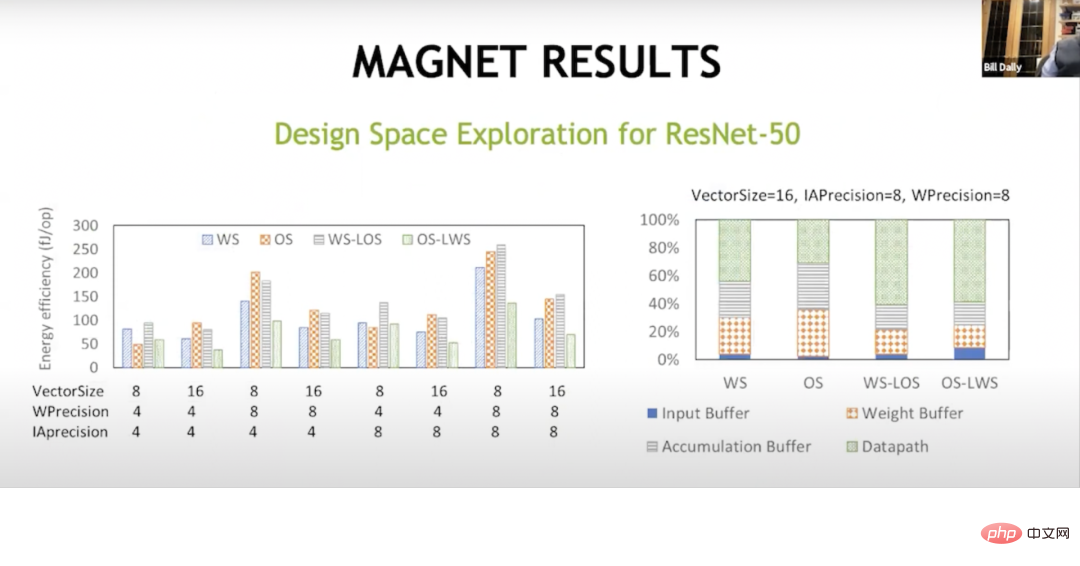

MAGNET RESULTS通过这种额外的缓存级别,我们最终取得了成功。这表明这里的数据流是不同的,而权重固定数据流最初是由Sze和Joel来完成的。你将大部分能量投到了数据路径以外的事情上,比如投入到累积缓冲区、权重缓冲区和输入缓冲区中。但通过这些混合数据流,权重固定,局部输出固定,输出固定,局部权重固定,能够在数学运算中获得几乎三分之二的能量,并且可以减少花在这些内存阵列中的能量,从而在内存层次结构的另一个层上进行处理。这使得现在的每瓦性能达到约为20 TOPS。

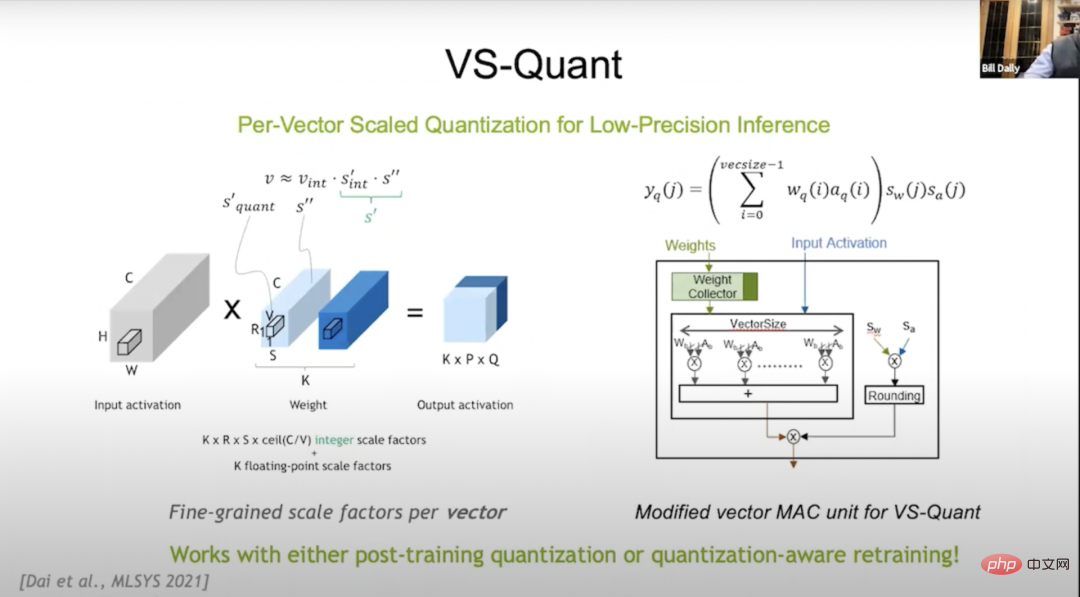

VS-Quant2021年,在MLSYS(The Conference on Machine Learning and Systems,机器学习与系统会议)会议上,我们引入了VS-Quant,以此来探索出一种在压缩比特数(这方面码本量化效果很好)和数学开销方面都很划算的量化方式。我们使用整数表示,但同时想要缩放该整数表示,以便可以表示出整数的动态范围。

但事实证明,如果你现在将其应用到整个神经网络,那么效果不会很好,因为神经网络上有很多不同的动态范围,所以VS-Quant的关键是:我们对一个相对较小的向量施加了一个单独的比例因子(scale factor),大约通过在32个权重上进行上述操作,动态范围会小得多。我们可以把这些整数放在上面,也可以对其调整优化。

也许我们没有将离群值准确地表示出来,但更好地表示出了其余数字。如此一来,我们就可以用相对低精度的权重和激活来换取较高的精度。所以我们现在有多个比例因子(scale factors ):一个是权重因子,一个是激活因子。

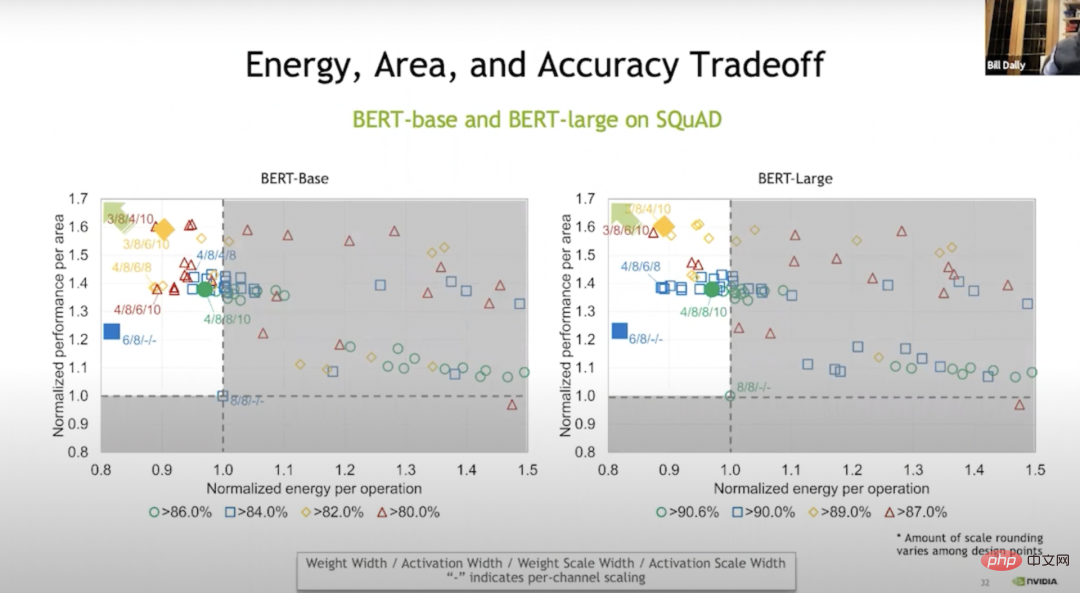

Energy, Area, and Accuracy Tradeoff我们基本上是在向量层级进行这些操作,结果如Bert-base所示。与不进行权重训练相比,我们可以通过训练在某些情况下节省20%的能量和70%的空间,上图的绿色表示基本上没有损失准确性;蓝色、橙色和红色表示准确性更高或更低。但即使在蓝色水平,准确性也相当高了。

通过VS-Quant和一些其他调整,我们在这些语言模型上进行了试运行。在语言模型上运行比在大约为120 TOPS/W的图像模型上运行要困难得多。

Accelerators所以对于加速器,要先做一个矩阵乘法器。我们需要提出一种平铺方法,一种采用神经网络的七个嵌套循环计算方法。本质上是将其中一些循环复制到内存系统的各层,以最大限度地重复使用每层的内存层次结构,并尽量减少数据搬运。

我们还研究了稀疏性,在压缩方面很不错。它基本上增加了内存带宽和通信带宽,减少了内存和通信的能量。稀疏性发展的下一个层次是:当你有一个零值,只需单独发送一条线表示零值,而不必在每个循环中切换到8或16位。

Ampere架构可以通过使用结构化稀疏来重用乘法器,这是一种很有效的方法,只需要几个多路复用器的开销(基本上可以忽略不计)。在进行指针操作时,我们也可以重用乘法器,从中可获得2倍的性能。数值表征(number representation)非常重要。我们从EIE开始(译者注:Efficient Inference Engine,韩松博士在ISCA 2016上的论文。实现了压缩的稀疏神经网络的硬件加速。与其近似方法的ESE获得了FPGA2017的最佳论文。),试图做码本,但这使得数学上的缩放很昂贵。

最后,在加速器里试验成功的技术最终会被运用到GPU中。这是一种很好的测试方式,我们认为,GPU是一个针对特定领域硬件的平台,它的内存系统非常好,网络流畅,能够让深度学习应用运行得非常快。

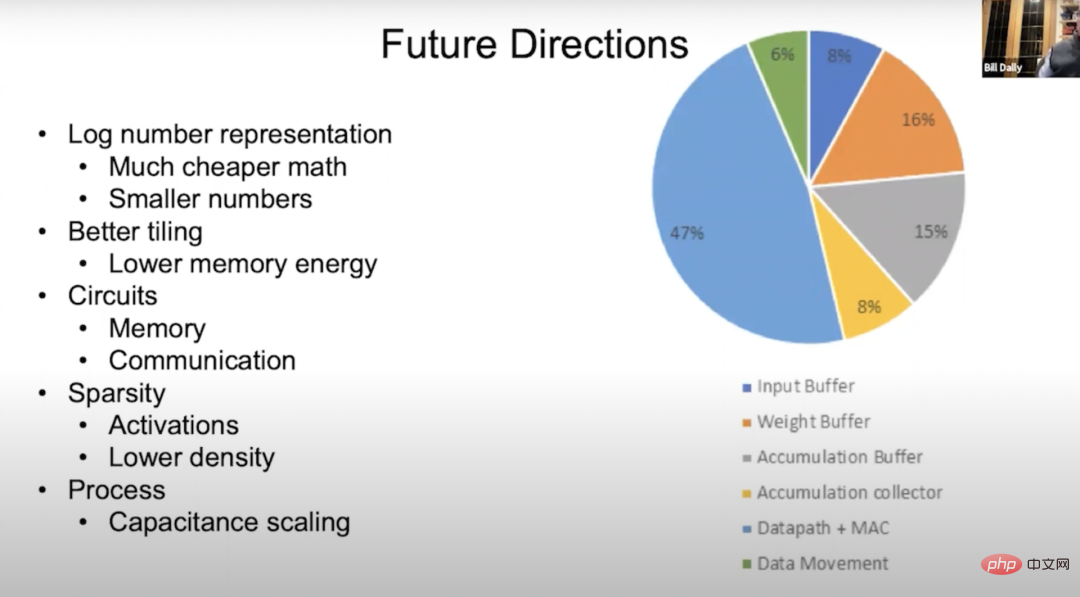

Future Directions接下来谈谈深度学习硬件的未来。上图是一个能量流向饼状图,从中可以看到大部分都流向于数据路径,其背后有大约50%是关于数学运算,所以我们想让数学运算的能量消耗更少;剩下很多流向内存和数据搬运。其中绿色的是数据搬运,其余部分是输入缓冲区、权重缓冲区、累加缓冲区和累加收集器,占比都有不同。 我们正在研究降低数学运算的能量消耗,最好的一个办法就是将其转移到对数系统。因为在对数系统中,乘法变成了加法,而加法的耗能通常要低得多。另一个办法是转为更小的数值,这一点可以通过VS-Quant实现。通过更精确地量化,我们可以用较低的精度数从神经网络中获得同等的精度。

我们希望能将平铺做得更好,比如在某些情况下,可能会在内存层次结构中添加更多层,这样就可以降低内存能量,也可以使内存电路和通信电路的效果更好。 在Ampere架构上,我们已经在结构化稀疏的工作是一个很好的开始,但我认为我们可以通过降低密度或选择多个密度来调整激活和权重,以此做得更好。 随着研究的深入,工艺技术也会带来一些电容缩放的进展。

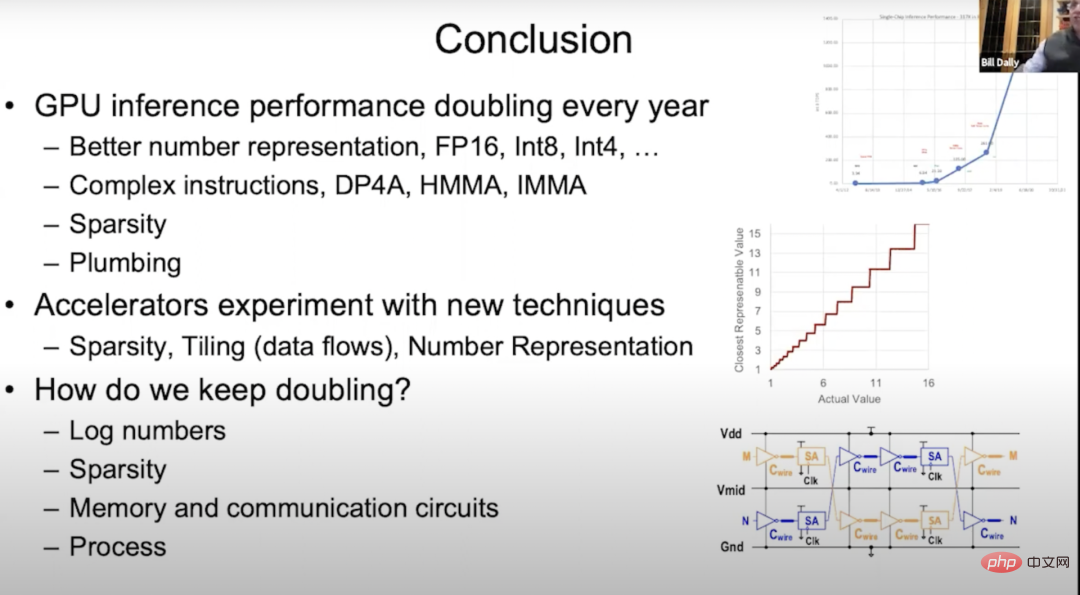

2012年发布Kepler架构以来,GPU的推理性能(inference performance)每年都在翻倍增长。发展到现在,很大程度上要归功于不断更好的数字表示。本次我们谈了很多内容,比如从Kepler架构的FP32到FP16到Int8再到Int4;谈到了通过分配指令开销,使用更复杂的点积;谈到了Pascal架构,Volta架构中的半精密矩阵乘累加,Turing架构中的整数矩阵乘累加,还有Ampere架构和结构稀疏。

关于Plumbing我谈得很少,但Plumbing却非常重要。通过Plumbing来布置片上内存系统和网络,由此可以充分利用强大的Tensor Cores(张量核心)。对于Tensor Cores来说,使其在Turing架构中每秒执行一千兆的操作,并将数据输入到执行通用基准测试中,以此来安排分支存储器、片上存储器和它们之间的互连互通以及正常运行,都非常重要。

展望未来,我们准备尝试将各种新技术应用到加速器中。前面提到,我们已经就稀疏性和平铺技术进行了多次实验,并在MAGNet项目中试验了不同的平铺技术和数值表示等等。但我们仍然倍感压力,因为深度学习的进步其实取决于硬件性能的持续提升,让GPU的推理性能每年都翻一番是一项巨大的挑战。

其实我们手里的牌打得差不多了,这意味着我们必须开始研发新的技术,以下是我认为值得关注的四个方向:

首先,研究新的数字表示,比如对数(Log number),以及比EasyQuant更加巧妙的量化方案;

其次,继续深入研究稀疏性;

然后,研究存储电路和通信电路;

最后,改良现有的工艺技术。

Dejan Milojicic:需要多大的矩阵卷积才能将Winograd算法转换成更高效的卷积实现?

Bill Dally:我认为,3×3的矩阵卷积就很高效。当然,卷积越大,效率越高。

Dejan Milojicic:高带宽存储器(High Bandwidth Memory, HBM)的内存带宽是如何计算的?是通过所有的GPU核同时访问内存吗?

Bill Dally:每个HBM堆栈都有一个单独的帧缓冲区,像Ampere架构有六个堆栈。我们的内存带宽是通过每个内存控制器以全带宽运行来计算的。各个GPU核之间都有一个缓存层,然后我们的片上网络的带宽是HBM带宽好几倍,所以基本上只需运行一小部分的流式多处理器就能使HBM达到饱和。

Dejan Milojicic:带有NVLink的分布式计算如何工作?谁来决定具体执行哪一个计算?在多个GPU上做scatter-gather时,哪些地方会产生开销以及会产生哪些开销?

Bill Dally:程序员会决定把数据和线程放在什么位置,而你只需在GPU上启动线程和数据以及确定它们的运行位置。采用NVLink进行连接的系统具备一大优势,那就是它是一个共享的地址空间,传输相对较小数据时的开销也相当小,所以我们在网络中采取集群通信。

通常情况下,如果你在深度学习中做数据并行,那么每个GPU都会运行相同的网络,但处理的是同一数据集的不同部分,它们会各自累积权重梯度,之后你再共享各个GPU上的梯度并累积所有梯度,然后添加到权重中。集群通信就非常擅长处理这样的工作。

Dejan Milojicic:我们到底是应该为所有应用创建通用的深度学习加速器,还是分别创建专用的加速器,比如视觉加速器或自然语言处理加速器?

Bill Dally:在不影响效率的情况下,我认为加速器当然越通用越好,英伟达的GPU在加速深度学习效率方面堪比专用加速器。真正重要的是,机器学习领域正在以惊人的速度向前发展。

几年前,大家还在使用循环神经网络处理语言,然后Transformer出现并以迅雷不及掩耳之速取代了RNN,转眼间所有人都开始使用Transformer进行自然语言处理。同样,就在几年前,每个人都在使用CNN来处理图像,虽然现在仍有不少人在使用卷积神经网络,但越来越多人开始使用Transformer来处理图像。

因此,我并不支持产品过度专用化或者为某一网络创建专用加速器,因为产品的设计周期通常需要持续好几年时间,而在此期间,人们很可能已经不再使用这种网络了。我们必须具备敏锐的眼光,及时洞察行业变化,因为它时刻都在以惊人的速度发展。

Dejan Milojicic:摩尔定律对GPU性能和内存占用有何影响?

Bill Dally:摩尔定律认为,晶体管成本会随时间逐年降低。今天,集成电路上可容纳的晶体管数量确实越来越多,芯片制程也实现了从16纳米到7纳米的飞跃,集成电路上的晶体管密度越来越大,但单个晶体管的价格却并未降低。因此,我认为摩尔定律有些过时了。

尽管如此,集成电路上能容纳更多的晶体管仍是一件好事,这样我们就能够建造更大规模的GPU。虽然大型GPU的能耗也会更高,价格也更加昂贵,但这总归是一件好事,因为我们能够构建一些从前无法构建的产品。

Dejan Milojicic:如果开发者比较重视PyTorch这样的框架,那么他们应该从硬件的进步中学习什么来让自己的深度学习模型运行更高效?

Bill Dally:这个问题很难回答。框架在抽象硬件方面做得很好,但仍然有一些影响模型运行速度的因素值得研究。我们可以尝试去做的是,当想出一项更好的技术时,比如更好的数值表示方法,可以尝试将各种不同的技术与框架相结合,看看哪种方法更加有效,这是研发工作不可或缺的环节。

Dejan Milojicic:英伟达是否正在实验新的封装方法?

Bill Dally:我们一直在对各种封装技术进行各种实验,弄清楚它们能做什么和不能做什么,以便在合适的时机将它们部署到产品。比如其中一些项目在研究多芯片模块,用焊接凸点、混合键合做芯片堆叠,其实有很多简洁的封装技术。

Dejan Milojicic:英伟达的Tensor Core和谷歌的TPU相比,谁更胜一筹? Bill Dally:我们对谷歌最新的TPU并不了解,但他们之前推出的TPU都是专用引擎,基本上都内置了大型的乘加器阵列。

TPU独立的单元来处理非线性函数和批量归一化(batch norm)之类的事情,但我们的方法是建立一个非常通用的计算单元流式多处理器(SM),只需非常通用的指令就可以让它做任何事情,然后再用Tensor Core来加速矩阵乘法部分。因此,Tensor Core和谷歌的TPU都有类似的乘加器阵列,只是我们使用的阵列相对较小。

Dejan Milojicic:英伟达最大的对手是谁? Bill Dally:英伟达从来不跟其他公司比较,最大的对手就是我们自己,我们也在不断地挑战自己,我认为这才是正确的态度。如果我们一味地把其他人视作竞争对手,反而放缓我们前进的脚步。不必过多关注其他人在做什么,我们真正应该关注的是哪些事情是可能实现的。我们所做的事就像在追求光速,我们更关注怎样才能做到最好,以及距离光速还有多远,这才是真正的挑战。

Dejan Milojicic:你对量子计算有何看法?量子模拟是深度学习挑战的自然延伸吗?

Bill Dally:2021年3月,我们发布了一款名为“cuQuantum”的软件开发工具包。Google之前也研制出了具有53个量子比特的计算机,并称自己实现了“量子优越性”。一些传统计算机无法完成的计算,用cuQuantum在五分钟内就能完成了。所以,如果想真正做到精准的量子算法,而不是今天的嘈杂中型量子(Noisy Intermediate-Scale Quantum,NIST)计算,GPU应该是最佳选择。

英伟达的传统GPU计算机是目前最快的量子计算机之一,阿里巴巴也在类似的经典计算中取得了不错的成绩,这恰好印证了我们的结论。我们对量子计算的看法是:英伟达不会因为这一技术领域的任何动态而感到惊讶。

实际上,我们还成立了一个研究小组来追踪量子计算领域的前沿动态,比如IBM宣布研制出了具有127个量子比特的芯片。我们也一直在跟踪量子比特数量和相干时间(coherence time)等方面的进展。

考虑到所需的量子比特数量、量子比特的准确性、噪音对量子的干扰以及量子纠错所需的开销,我认为未来五到十年内,量子计算都无法实现商用。 我最乐观的看法是,大概五年后,人们将开始进行量子化学模拟,这应该最有可能做到的。但在那之前,还有很多物理上的难题需要解决。很多人还没有意识到,量子计算机就是模拟计算机,而模拟计算机需要非常精确且易于隔离,否则任何与环境的耦合都会导致结果不一致。

Dejan Milojicic:在你看来,机器何时才能达到通用人工智能(AGI)的水平?

Bill Dally:我对这个问题的看法比较消极。试看一些比较成功的人工智能用例,例如神经网络,其实它本质上就是通用函数拟合器。神经网络可以通过观察来学习一个函数,所以它的价值还是体现在人工感知而不是人工智能。

虽然我们目前已经取得了不错的成果,但还是可以继续研究如何使用人工智能和深度学习来提高生产力,从而改善医疗、教育,给人们带来更加美好的生活。其实,我们不需要AGI来做到这些,而应该重视如何最大程度地利用现有技术。距离AGI还有很长的路要走,我们也必须弄清到底什么是AGI。

以上是英伟达首席科学家:深度学习硬件的过去、现在和未来的详细内容。更多信息请关注PHP中文网其他相关文章!