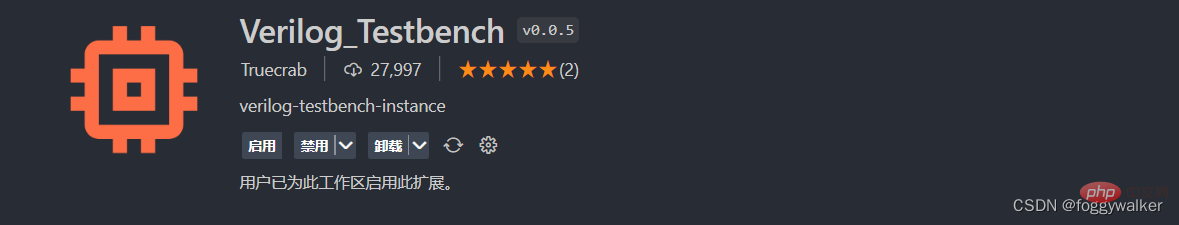

VSCodeVerilog 환경을 구성하는 방법은 무엇입니까? 다음 기사에서는 VSCode가 Verilog를 원활하게 작성할 수 있도록 세 가지 플러그인을 권장합니다. 세 가지 플러그인은 코드 프롬프트 + 자동 인스턴스화 + 서식 지정을 실현할 수 있습니다.

【추천 학습: vscode 튜토리얼, 프로그래밍 비디오】

달성 가능한 기능:

플러그인 구성

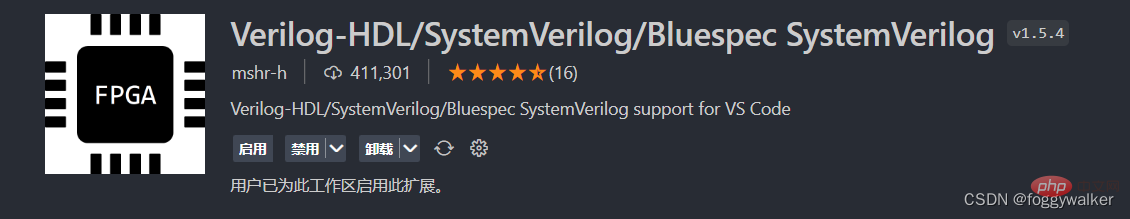

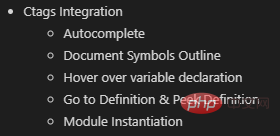

Verilog HDL/SystemVerilog 플러그인 시작 페이지에 설명된 대로 Ctags 기능이 지원됩니다.

구성 단계:

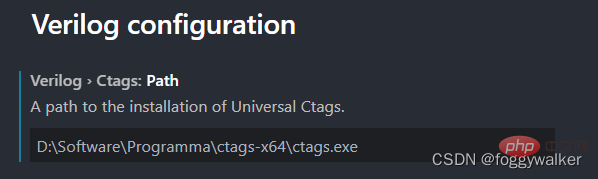

최신 버전의 ctags를 다운로드하세요. 이전 버전의 일부 기능은 충분하지 않습니다. Windows는 x64 버전을 선택할 수 있습니다.

ctags.exe 경로를 시스템 환경으로 설정하세요. 변수

플러그인 설정 ctags 경로 구성

VSCode를 다시 시작하세요.

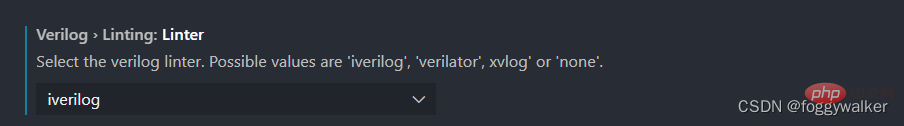

다음을 포함하여 다른 컴파일러를 선택할 수 있습니다.

iverilog xvlog( vivado)

xvlog( vivado)

modelsim

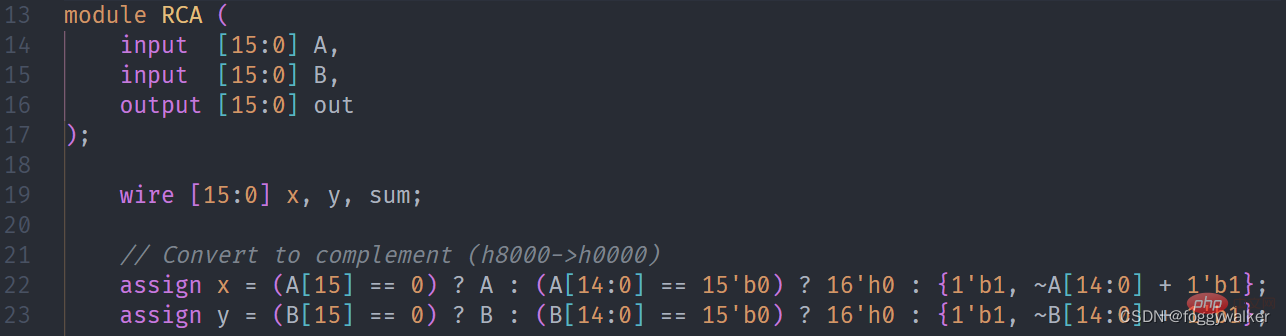

Verilog 및 SV와 같은 구문 강조를 지원합니다.

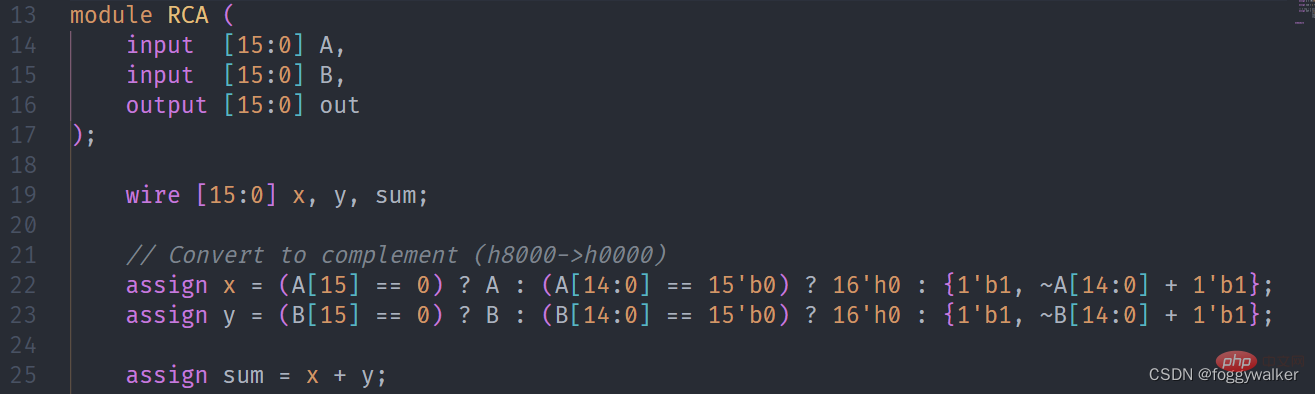

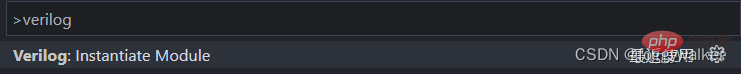

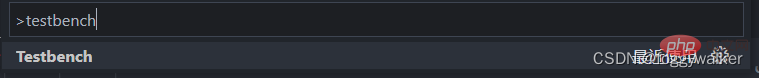

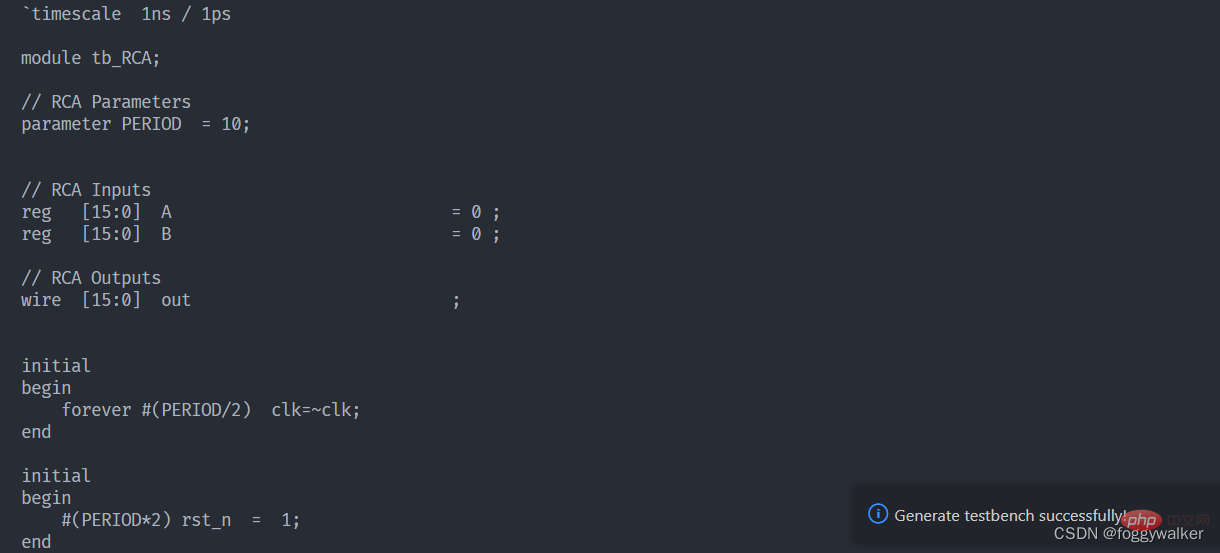

Shift+ctrl+p 입력 Verilog를 사용하면 자동으로 모듈을 직접 인스턴스화할 수 있습니다.

SystemVerilog 및 Verilog Formatter

효과는 매우 좋으며 광범위한 사용자 정의 형식 매개변수를 지원합니다. 개인적으로는 Verilog 형식보다 사용하기 더 쉽다고 생각합니다.

광범위한 사용자 정의 형식 매개변수를 지원합니다. 개인적으로는 Verilog 형식보다 사용하기 더 쉽다고 생각합니다.

기능 구현 가능

사용자 지정 형식

사용자 지정 매개 변수 설정 테이블

common/formatting/basic_format_style_init.cc의 플래그:

--column_limit(서식을 지정할 때 유지해야 할 대상 줄 길이 제한.);

기본값: 100;

--indentation_spaces(각 들여쓰기 수준에 이 만큼의 공백이 추가됩니다.);

기본값 : 2;

--line_break_penalty (각 도입된 라인

break에 대한 솔루션에 페널티가 추가됩니다.); 기본값: 2;

--over_column_limit_penalty(페널티 최소화를 위해 이는 열 제한을 초과하는

기준 페널티 값을 나타냅니다. 이 한도를 초과하는 각 문자에 대해 추가 페널티

1개가 발생합니다); 기본값: 100;

--wrap_spaces (각 래핑 수준은 이만큼의 공백을 추가합니다. 이는 오픈 그룹 섹션 이후의 첫 번째 요소가

래핑될 때 적용됩니다. 그렇지 않으면

들여쓰기 수준이 오픈 그룹의 열 위치로 설정됩니다.

연산자.); 기본값: 4;

external/com_google_absl/absl/flags/parse.cc의 플래그:

--flagfile(플래그를 로드할 파일의 쉼표로 구분된 목록); 기본값: ;

--fromenv(환경에서 설정할 플래그의 쉼표로 구분된 목록 [use

'export FLAGS_flag1=value']); 기본값: ;

--tryfromenv(환경이 있는 경우

환경에서 설정하려고 시도할 플래그의 쉼표로 구분된 목록); 기본값: ;

--undefok (프로그램이 해당

이름을 가진 플래그를 정의하지 않더라도

명령줄에 지정할 수 있는 쉼표로 구분된 플래그 이름 목록); 기본값: ;

verilog/formatting/format_style_init.cc의 플래그:

--location_statement_alignment(다양한 할당 형식 지정:

{align,flush-left,preserve,infer}); 기본값: infer;

--case_items_alignment (케이스 항목 형식 지정:

{align,flush-left,preserve,infer}); 기본값: infer;

--class_member_variable_alignment (클래스 멤버 변수 형식 지정:

{align,flush-left,preserve,infer}); 기본값: 추론;

--compact_indexing_and_selections(

인덱싱/비트 선택 연산자 내부에서 압축 이진 표현식 사용); 기본값: true;

--distribution_items_alignment (배포 항목 정렬:

{align,flush-left,preserve,infer}); 기본값: infer;

--enum_signment_statement_alignment(열거형 할당 형식:

{align,flush-left,preserve,infer}); 기본값: infer;

--expand_coverpoints (true인 경우 항상 커버포인트를 확장합니다.); 기본값: false;

--formal_parameters_alignment(형식 매개변수 형식:

{align,flush-left,preserve,infer}); 기본값: infer;

--formal_parameters_indentation (형식 매개변수 들여쓰기: {indent,wrap});

기본값: Wrap;

--module_net_variable_alignment (순/변수 선언 형식:

{align,flush-left,preserve,infer}); 기본값: infer;

--named_parameter_alignment(실제 매개변수라는 형식:

{align,flush-left,preserve,infer}); 기본값: 추론;

--named_parameter_indentation (이름이 지정된 매개변수 할당 들여쓰기:

{indent,wrap}); 기본값: Wrap;

--named_port_alignment(이름이 지정된 포트 연결 형식:

{align,flush-left,preserve,infer}); 기본값: infer;

--named_port_indentation (이름이 지정된 포트 연결 들여쓰기: {indent,wrap});

기본값: Wrap;

--port_declarations_alignment (포트 선언 형식:

{align,flush-left,preserve,infer}); 기본값: infer;

--port_declarations_indentation (포트 선언 들여쓰기: {indent,wrap});

기본값: Wrap;

--port_declarations_right_align_packed_dimensions (true인 경우 정렬이 활성화된 컨텍스트의 포장

차원은 오른쪽으로 정렬됩니다.);

default: false;

--port_declarations_right_align_unpacked_dimensions(true인 경우 정렬이 활성화된 컨텍스트의 압축되지 않은

차원이 오른쪽으로 정렬됩니다.);

default: false;

--struct_union_members_alignment(구조체/공용 구조체 멤버 형식:

{align,flush- 왼쪽, 보존, 추론}); 기본값: infer;

--try_wrap_long_lines(true인 경우 포맷터가 줄 바꾸기를 최적화하려고 시도하도록 합니다

줄 바꿈이 필요한 곳에서 줄 바꿈 결정을 시도하고, 그렇지 않으면 서식을 지정하지 않은 상태로 둡니다.

이는 피해 위험을 줄이기 위한 단기 조치입니다.); 기본값: false;

verilog/parser/verilog_parser.cc의 플래그:

--verilog_trace_parser(Trace Verilog 파서); 기본값: 거짓;

verilog/tools/formatter/verilog_format.cc의 플래그:

--failsafe_success(true인 경우

입력 오류나 내부 오류가 있더라도 항상 0 상태로 종료합니다. 모든 오류 조건에서 원본

텍스트는 항상 보존됩니다. 이는 안전 동작이 성공으로 간주되어야 하는 서비스 배포에 유용합니다.) 기본값: true;

--inplace(true인 경우 성공 조건에서 입력 파일을 덮어씁니다.);

기본값: false;

--lines(형식을 지정할 특정 줄, 1 기반, 쉼표로 구분, N-M 포함

범위, N은 N-N의 약자입니다. 기본적으로 지정하지 않으면 모든 줄에 서식이 적용됩니다(반복 가능, 누적). 기본값: ;

--max_search_states(라인

줄 바꿈 최적화 중에 탐색되는 검색 상태 수를 제한합니다.); 기본값: 100000;

--show_equally_optimal_wrappings(true인 경우 여러 최적

솔루션을 찾았을 때 인쇄하지만(stderr) 정상적으로 계속 작동합니다.);

기본값: false;

--show_inter_token_info(true인 경우 show_token_partition_tree와 함께

공백 및 구분 페널티와 같은 토큰 간 정보를 포함합니다.);

기본값: false;

--show_largest_token_partitions (> 0인 경우 토큰 파티셔닝을 인쇄한 다음

출력 형식을 지정하지 않고 종료합니다.); 기본값: 0;

--show_token_partition_tree (true인 경우 토큰

분할 후 진단을 인쇄한 다음 출력 형식을 지정하지 않고 종료합니다.); 기본값: false;

--stdin_name('-'를 사용하여 stdin에서 읽을 때 진단 목적으로 대체

이름을 제공합니다. 그렇지 않으면 무시됩니다.);

기본값: "

--verbose (좀 더 자세히 설명해주세요.); 기본값: false;

--verify_convergence(true이고

--lines를 사용하여 점진적으로 형식을 지정하지 않는 경우 형식이 지정된 출력을 다시 형식화하면 더 이상 변경 사항이 발생하지 않는지 확인합니다

, 즉 형식이 수렴됩니다.); 기본값: true;

모든 플래그 목록을 얻으려면 --helpfull을 시도하거나 --help=substring은 이름, 설명 또는

플래그에 대한 도움말을 표시합니다.

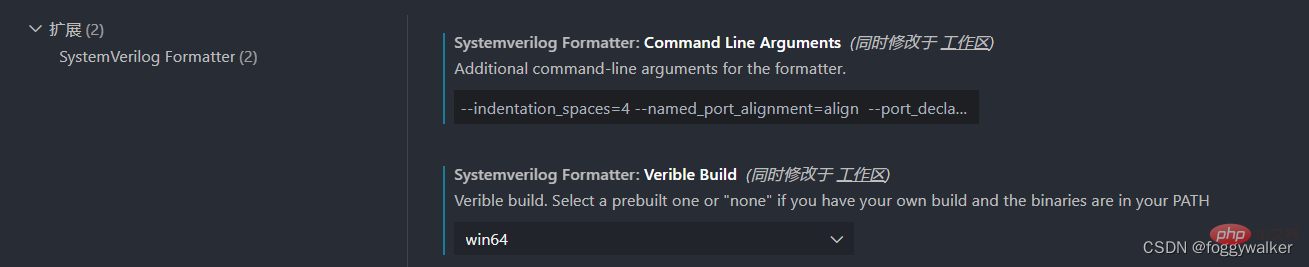

插件配置

如果是windows,systemverilogFormatter.veribleBuild设置为win64

如果是windows,systemverilogFormatter.veribleBuild设置为win64

systemverilogFormatter.commandLineArguments可以自定义格式化参数,下face放上我自己用的参数,可以实现大分常用代码段实现对齐。

--indentation_spaces=4 --named_port_alignment=align --ort_declarations_alignment=align --module_net_variable_alignment=align

如何使사용?如何格式化?andvscode内置格式化一样,直接shift+ctrl+f就可以格式化文件,ctrl+k可以格式化选定内容。

值得注意的是,由于这个插件也是이 完善中,还是存在part问题的입니다. ㅋㅋ将最后一个端口加上","就不能格式化了。

vscode基础教程 !

!

위 내용은 VSCode에서 Verilog 환경을 구성하는 방법은 무엇입니까? 코드 프롬프트 + 자동 인스턴스화 + 포맷팅 플러그인 공유의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!