When you mention ChatGPT, what do you think of? When you think of chips, what do you think of? You can write down the first word that comes to your mind. After reading this article, it will definitely change your opinion. If you are a technology enthusiast, your first impression is that ChatGPT is a highly intelligent conversation model that can talk to people. The chip industry is a complex whole, with not only upper-level architecture designers, but also lower-level processes. film engineer. You might not combine the two because they seem so unrelated.

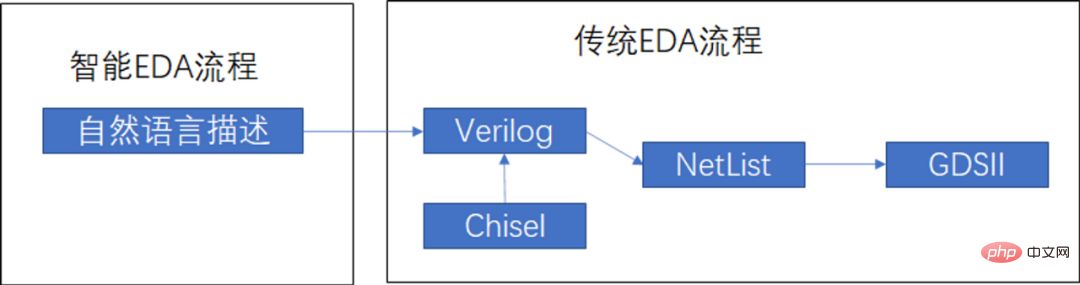

But in fact, the unique code generation capability of the ChatGPT model greatly accelerates the speed of chip design. The transformation wave from traditional EDA (Electronic Design Automation) to smart EDA is about to begin. In today's article, we will take a look at how traditional EDA evolves into smart EDA driven by ChatGPT, and how ChatGPT drives innovation in the chip design industry chain. .

First of all, let’s look at an application of ChatGPT at the forefront of the chip industry: the quantum control processor is the core control part of the quantum computer. The code of a quantum control processor synthesized using ChatGPT is as follows.

module QuantumControlProcessor ( input clk, input reset, input [7:0] instruction, input [7:0] control, output reg [7:0] qubit_pulse, output reg [7:0] timing_pulse ); // 此处因为篇幅原因省略实现 endmodule

In fact, this code may have some minor problems. For example, ChatGPT cannot achieve timing control well and will waste clock cycles, but this code can be correct. compiles and is a valid design solution. Maybe you will be surprised, how is this done? What are the prospects for this? The rest of this article will give you the answer.

ChatGPT will provide enough reusable code for the chip industry

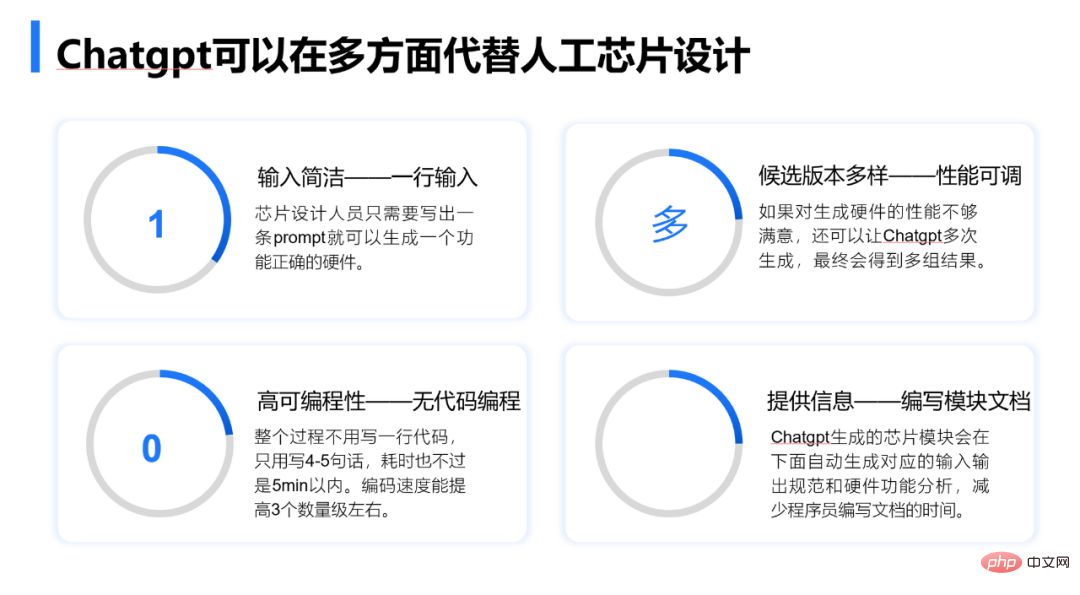

The huge amount of design code required by the chip industry urgently requires an efficient development tool. Chip design is an industry that requires a lot of code accumulation. For example, the core open source code of Alibaba's Xuantie OpenC910 is about 351KLOC. As shown in Figure 1, the industry generally starts design from the top verilog, using EDA's front-end and back-end tools to generate layouts. The writing of verilog requires design timing, which is usually more complicated, so ChatGPT can reduce a lot of labor costs by generating this piece of code. The timing requirements of the chip are relatively strict, so there are also a large number of timing-related modules with relatively fixed functions, such as AXI interface, FIFO, etc. These modules can all use ChatGPT to reduce labor costs. Although there are currently new hardware design languages such as Chisel, Spatial, and MyHDL, these languages are largely subject to the limitations of the host language and cannot describe circuits in a way that is close to natural language.

ChatGPT shows excellent expressiveness in code generation. Just give it a task prompt and the corresponding code will be automatically generated. Compared with the synthesis of software and algorithms, hardware design code does not have the diversity of scenarios like software business code, and although its parameterization and timing control are complicated compared to human cognitive abilities, there are fixed patterns to follow, so ChatGPT has more obvious advantages in automatically generating hardware design code. It has good induction capabilities for existing hardware and can accurately extract parameterizable configuration points in the design template.

The author’s instructor, Dr. Wang Ying, associate researcher at the Institute of Computing Technology, Chinese Academy of Sciences, believes that even a fully industrialized ChatGPT will not be able to bring the ideal fully automated design capabilities in the short term, but with the The trend of cloud EDA is expected to soon serve as a design assistant to greatly improve design verification efficiency and lower development thresholds, especially for teaching work. It will bring important changes. In addition, the level of automation demonstrated by ChatGPT in various processes is not unknown in the EDA field. Compared with other SOTA technologies, ChatGPT has natural advantages in terms of completeness and natural interaction. Finally, ChatGPT has verified the potential of large models in the field of automated chip design, and can drive developers to further design the Prompt paradigm on top of it, thereby leaving room to further improve the functional accuracy of the design and the performance of the generated chips.

ChatGPT’s intellectual level in the field of chip design far exceeds previous similar work

ChatGPT 真的有替代人工的准确性吗?

ChatGPT 和之前最好的代码自动生成的方法比起来好了多少呢?

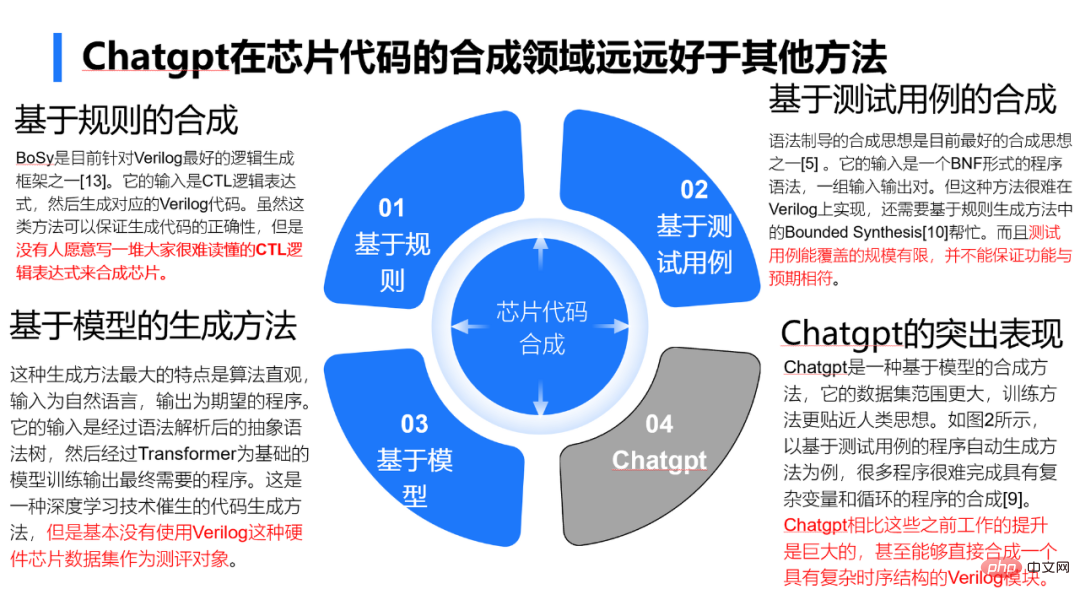

可以把之前的代码生成方法分为三类,一类是以编程语言社区为代表的基于规则 [11,12,13] 的方法,第二类是基于测试用例的生成方法 [5, 6, 7, 8, 9, 10],第三类是以自然语言处理社区为代表的基于文本和模型的生成方法 [1, 2, 3, 4]。

表:比较 OpenAI 两种最新模型用于代码生成

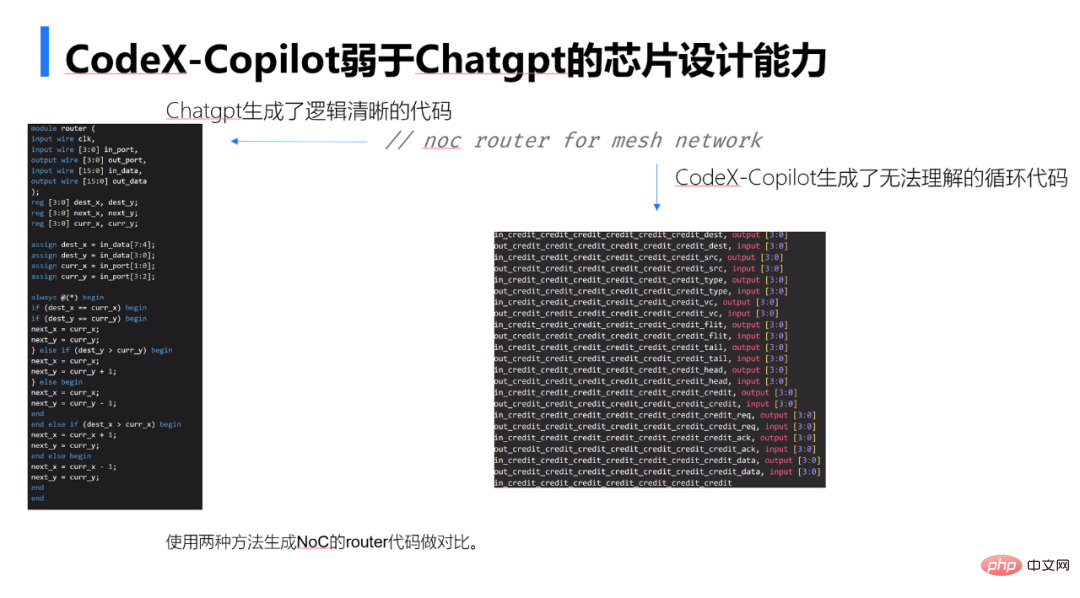

ChatGPT 和 CodeX 都是 OpenAI 公司基于 GPT-3 研发的模型,从上面的分析中可以看出,ChatGPT 的范围更广,并且 Copilot 的用途单一,仅仅为代码补全。这就为基于 ChatGPT 开发智能代码相关工具提供了更广阔的空间。

ChatGPT 极大地驱动了智能 EDA 技术的发展

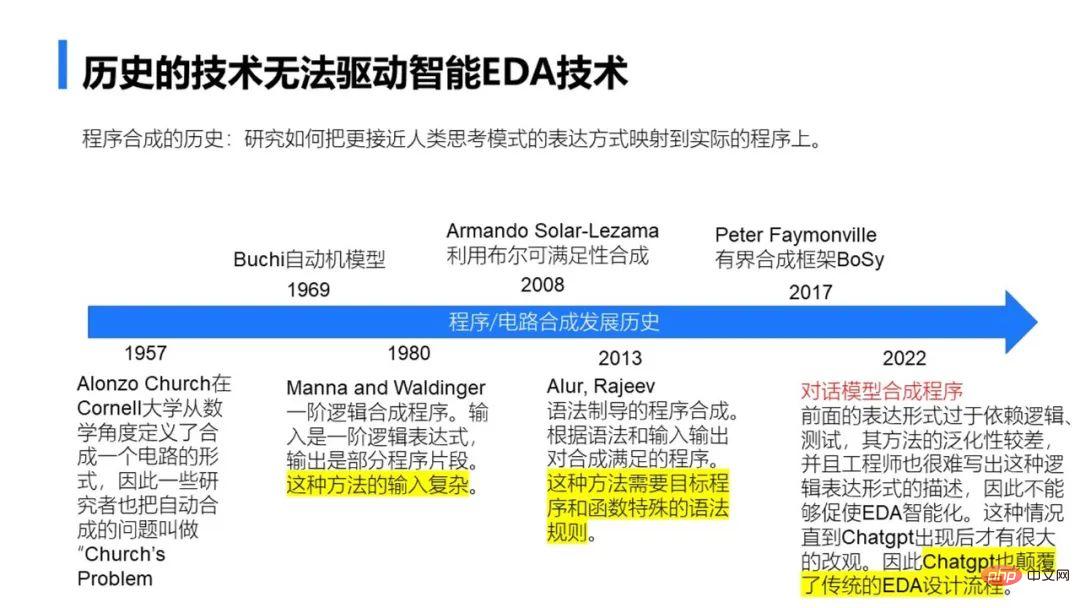

在 ChatGPT 出现之前,就有许多自动化代码生成方式,他们为什么不能够驱动智能 EDA 技术呢?

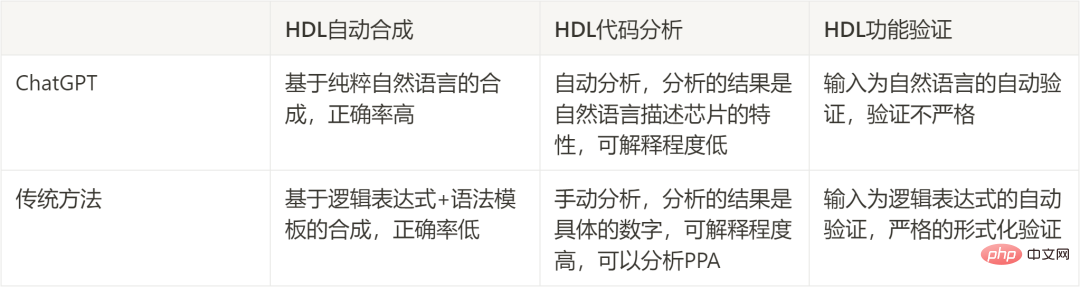

ChatGPT 能够远远地超越传统方法,并且它可以做到零样本学习(Zero-shot learning),相比传统的程序合成并不需要专门的训练(因为 OpenAI 已经完成了),并且配合细致的功能描述,他庞大的知识储备也可以使能高正确率的代码生成。如表 1 所示,ChatGPT 将会逐渐演变为芯片前端的自动化流程中极为关键的一步,在未来很有可能演变成为继 HLS 开创 C 语言设计芯片后的又一种新的范式。在后文,我们将会介绍如何使用 ChatGPT 做 Verilog 的代码生成。

表 1:ChatGPT 在芯片自动生成各个领域的开创性创新(以 Hardware Design Language 为例,软件语言可以参照分析)

如何使用 ChatGPT 生成芯片代码

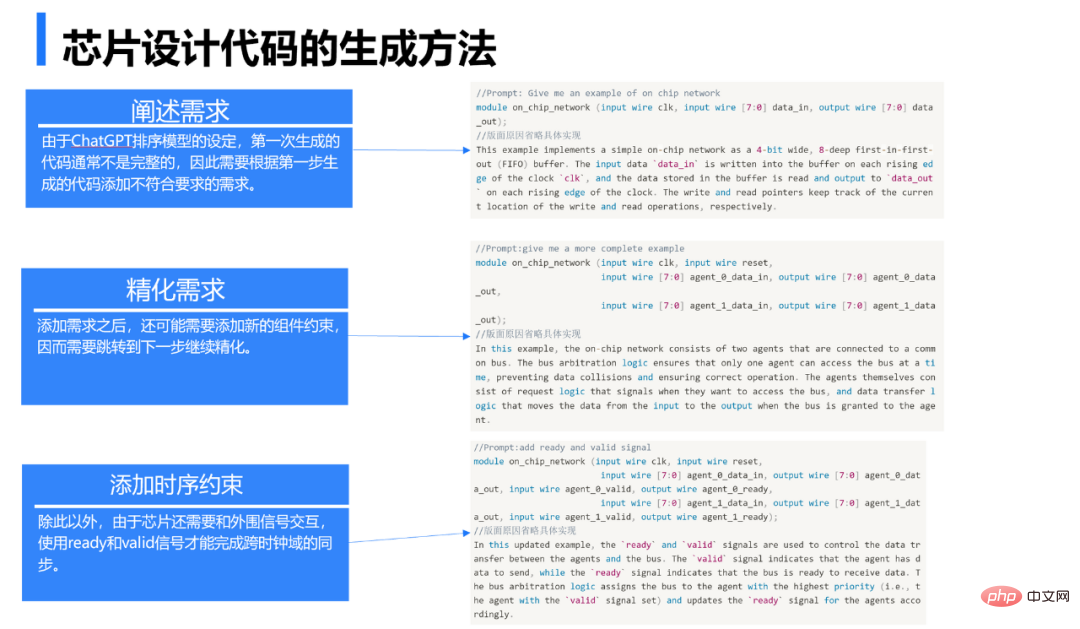

与芯片设计相关的程序合成方法包含两类,高层次程序生成和时序相关硬件描述代码生成。高层次程序生成可以生成 HLS 等不具有显式时序控制的 C/C++ 代码等,而低层次程序生成可以生成具有显式时序控制的 Verilog 代码。由于 HLS 在实际工业界设计芯片时较少采用,因此我们采用 Verilog 作为主要的目标语言。对于 ChatGPT 而言,我们以自然语言描述作为输入,就可以获得符合要求的芯片描述代码。具体来说,应该如何做呢?我们以 Verilog 为例介绍如何用 ChatGPT 生成代码。

基于 ChatGPT 的通用生成步骤

act as a professional verilog programmer

因为 ChatGPT 是个通用的代码生成工具,而 Verilog 是个专用领域,我们需要先 “催眠” ChatGPT,使得它能够生成 Verilog 程序。向 ChatGPT 中输入下面的 prompt,之后的生成都会是以 Verilog 代码为基础的。

我们接下来的部分都是以片上网络 NoC 模块为例阐述代码生成方法的通用步骤。

Due to limited space, the complete code generated by ChatGPT will not be listed here. But we can see that there are many different ways of understanding the keyword On-Chip Network, and ChatGPT has chosen a bus-based understanding method. If we want other ways of semantic understanding, we should explore different ways of inputting questions.

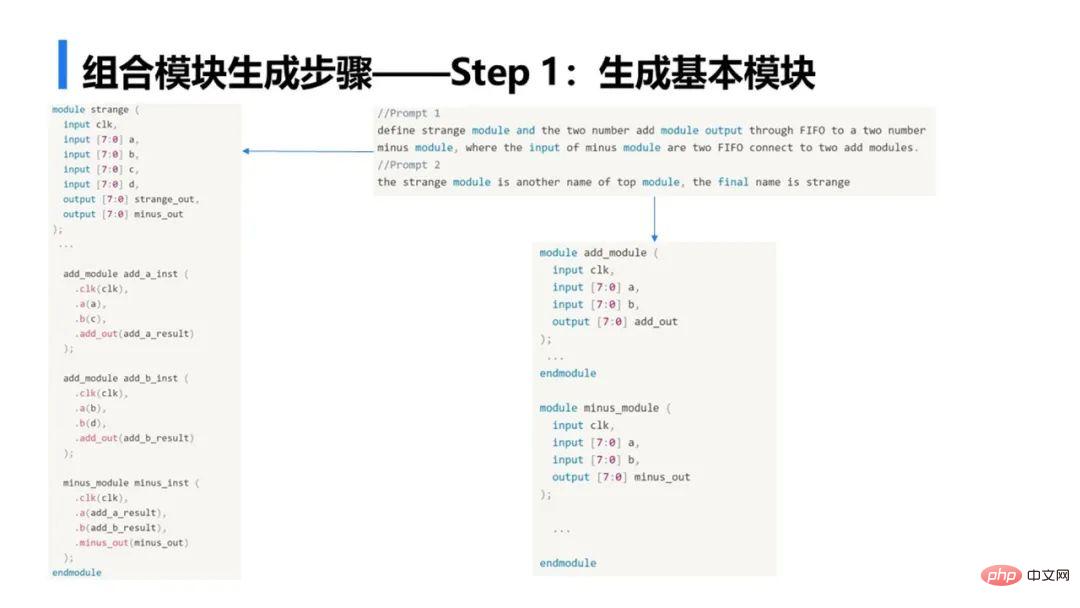

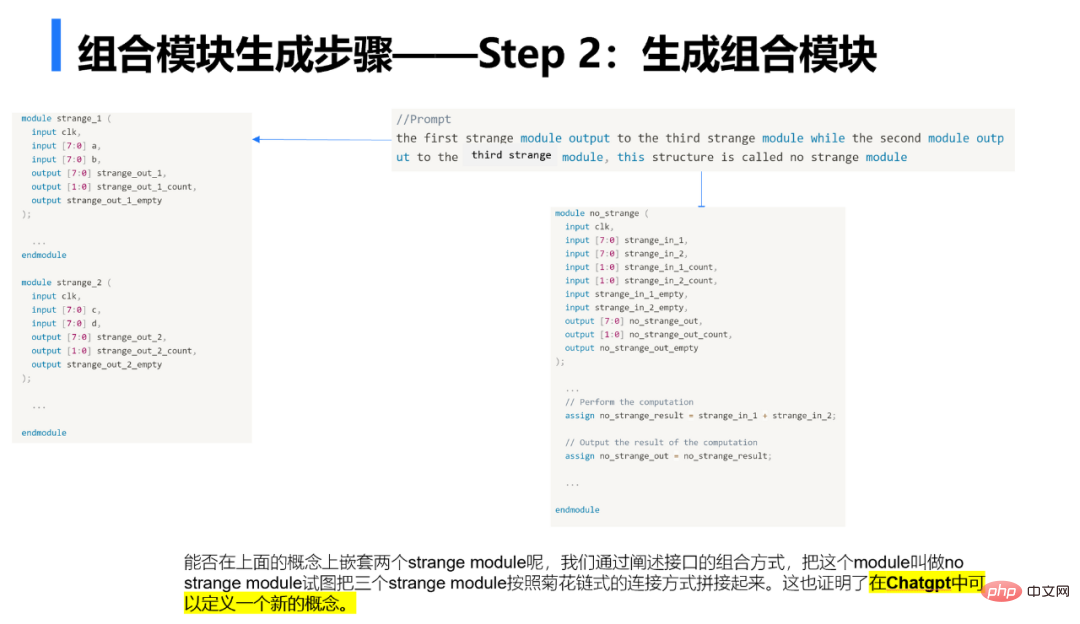

Steps to combine and generate modules

Only limited modules were generated before, but can the modules be combined? Our goal is to combine two strange modules that do not exist originally into a no strange module. A top-level module strange is generated below. There are two adders on the bottom layer, and their outputs are connected to a subtractor. We call this strange module.

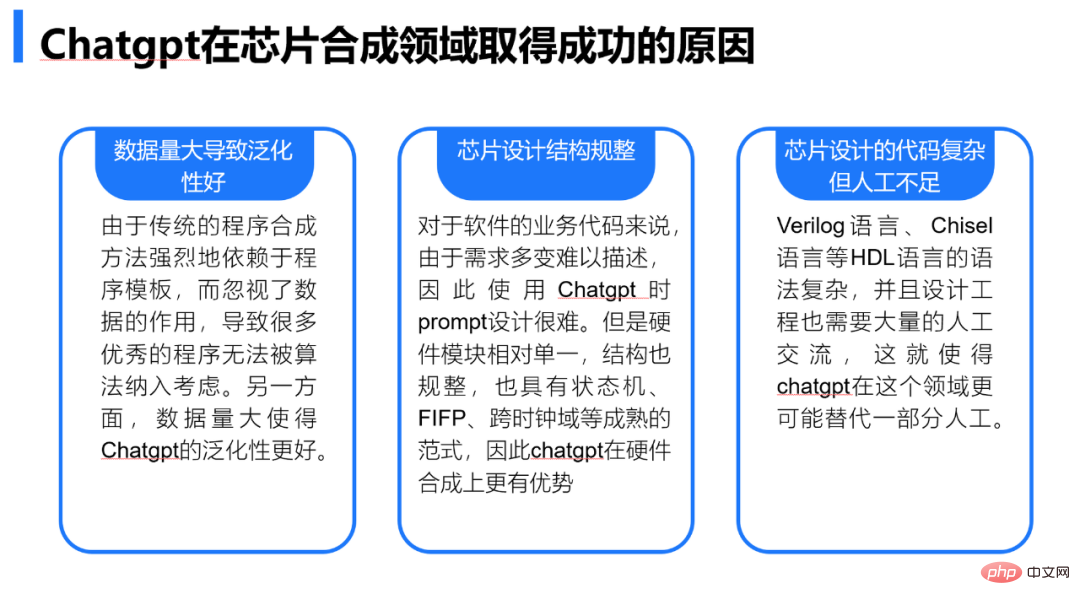

#Why is ChatGPT successful in the field of chip generation

ChatGPT’s success in chip synthesis should be attributed to its understanding of codes and accurate recognition of natural language semantics.

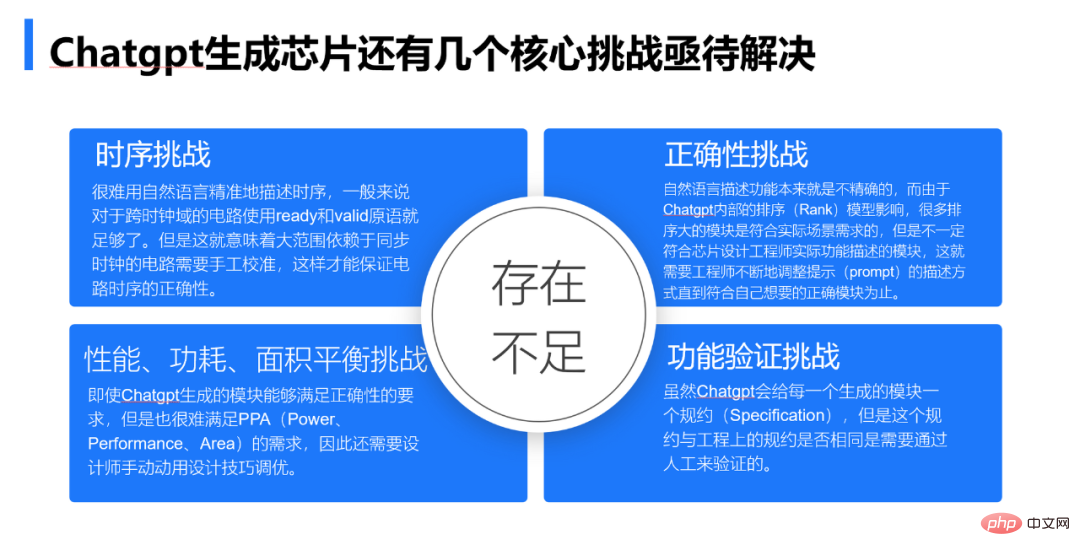

ChatGPT Is everything ready to generate the chip design?

Although the ChatGPT model can complete part of the front-end work of chip design, there are still the following challenges, which require joint tuning of manual and EDA tool chains to generate a chip that meets the specifications.

##How the silicon industry responds to the smart EDA crisis

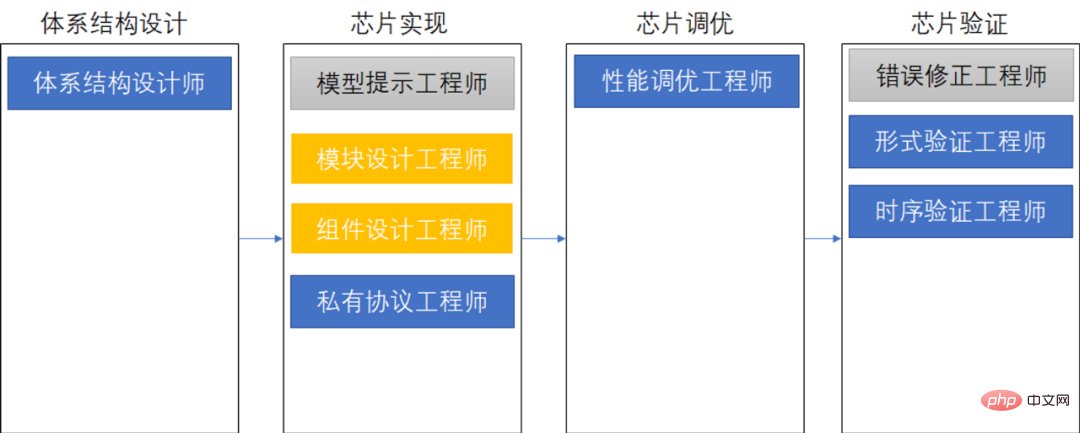

ChatGPT As an intelligent EDA process, it is both a crisis and an opportunity. It can replace part of the EDA front-end work, but because the EDA back-end relies heavily on determinism and analysis of details to obtain a better optimization structure, it is difficult to support EDA back-end optimization work. But it also creates new positions, such as possible model prompt engineers and error correction engineers.

Figure 5: Alternatives by engineer position

In order to more clearly classify the substitutability trends in the silicon industry in different positions, we have divided it into four stages from top to bottom according to the EDA process, namely the architecture design stage - chip code implementation stage - chip PPA Tuning phase - The chip verification phase is shown in Figure 5. Note that the chip tuning here refers to the tuning achieved on the front end by changing some hardware structures and algorithms, so it is listed before chip verification. Blue boxes represent positions that are difficult to replace, yellow boxes represent positions that are easily replaced, and gray boxes represent newly added positions. The following analysis of substitutability according to specific processes reveals why engineers in some positions are easily replaced by ChatGPT, while engineers in some positions are difficult to be replaced by ChatGPT.Researcher Han Yinhe, director of the Intelligent Computing Center of the Institute of Computing Technology, Chinese Academy of Sciences, believes that ChatGPT can not only help speed up the chip design process, but also bring a series of challenges to the chip itself, which may be the current hot topics such as storage and computing. Technologies such as one-piece, chip-to-chip integration and large-chip architecture bring eagerly awaited killer applications.

Future Development Trend

Under the wave of intelligent EDA, some positions are inevitable will be replaced, then in what order will they be replaced in the future? From the perspective of front-end and back-end distribution, the back-end is highly irreplaceable due to its detailed tasks such as layout design. For the front-end, the first replacement is the module engineer in chip implementation, because from the practice of generating chips above, it can be found that the basic module code generation part is the most intuitive. The replacement positions that will appear after it are component design engineers. This part will be replaced after engineers become familiar with using ChatGPT to assemble modules. For other engineers, ChatGPT is more of an auxiliary value rather than a complete replacement.

Thus we can see that the higher the level, the less likely it is to replace the parts involving architectural abstraction; the lower the level, the less likely it is to replace the parts involving correctness. The replacement order of the middle parts will be bottom-up, from basic modules to upper-level components.

The policy must seize the opportunity of smart EDA

Self-reliance and fully absorbing the world Frontier is not without contradiction. There are complex reasons why traditional EDA and large models debuted at OpenAI but other companies have not yet caught up. However, policies still need to separate a hand to divert some overheated capital from projects that solve traditional EDA and large model problems, and encourage companies to seize the early stage of intelligent EDA development when industry barriers are small, bravely enter the industry, and construct new products. technical barriers. Only in this way can we solve the problem of being constantly replaced by new technologies. Otherwise, the influx of overheated capital into mature industries will cause a decline in the rate of return on capital. At the same time, innovative technologies will not be able to obtain higher financial support, causing innovative companies to dare not try and make mistakes, which will virtually increase the trial and error costs of innovative companies, making Innovative companies prefer market-proven technologies. Therefore, policies should appropriately encourage companies to develop derivative technologies based on large models such as ChatGPT, especially since large models have demonstrated strong code generation capabilities. Companies based on intelligent EDA technology should seize the opportunity.

The investment focus of the capital market should shift from the large model itself to its derivative technologies

In the field of information technology , advanced technologies continue to move from general to specialized, and gradually move towards derivative technologies based on previous technologies, most obviously in the field of processor design. In the last century, CPUs became very popular, creating high-performance computers. At the beginning of this century, GPUs gradually became popular, driving the development of games. In the past ten years, NPUs have begun to step onto the stage, enabling energy-efficient neural network training. and reasoning. It can be inferred that when the large model matures, its derivative technologies will also come to the stage in the next few years.

Intelligent EDA technology is a derivative of large model technology. Although investment in derivative technologies does not seem to be advantageous at the beginning, from an economic point of view, the return on investment will be higher until that technology is launched and forms a technical barrier. As large model technologies such as ChatGPT mature, investment in enterprises will experience diminishing marginal effects. Individual investors and institutional investors should recognize the investment rules of information technology and gradually turn their attention to the derivative fields of large models, especially the application of algorithms based on large models in the chip field. Industrial practitioners should make full use of the advantages of large funds established in my country for the fields of artificial intelligence and integrated circuits, and actively apply for funds that intersect artificial intelligence and EDA. Therefore, whether from the perspective of industrial policy or investment rules, the field of intelligent EDA is very necessary and should become an investment target for Chinese investors.

Code generation based on text model

[1] Zhangyin Feng, Daya Guo, Duyu Tang, Nan Duan, Xiaocheng Feng, Ming Gong, Linjun Shou, Bing Qin, Ting Liu, Daxin Jiang, and Ming Zhou. 2020. [CodeBERT: A Pre-Trained Model for Programming and Natural Languages]. In Findings of the Association for Computational Linguistics: EMNLP 2020, pages 1536–1547, Online. Association for Computational Linguistics.

[2] [GRAPHCODEBERT: PRE-TRAINING CODE REPRESENTATIONS WITH DATA FLOW]

[3] [CodeT5: Identifier-aware Unified Pre-trained Encoder-Decoder Models for Code Understanding and Generation]

[4] [UniXcoder: Unified Cross-Modal Pre-training for Code Representation]

基于测试用例的代码生成

[5] Rajeev Alur, Rastislav Bodík, Garvit Juniwal, Milo M. K. Martin, Mukund Raghothaman, Sanjit A. Seshia, Rishabh Singh, Armando Solar-Lezama, Emina Torlak, Abhishek Udupa, [Syntax-guided synthesis], 2013

[6] Peter-Michael Osera, Steve Zdancewic, [Type-and-example-directed Program Synthesis], 2015

[7] John K. Feser, Swarat Chaudhuri, Isil Dillig, [Synthesizing Data Structure Transformations from Input-output Examples], 2015

[8] Armando Solar-Lezama, [Program Synthesis by Sketching], 2008

[9] [Kensen Shi], [Jacob Steinhardt], [Percy Liang], FrAngel: Component-Based Synthesis with Control Structures, POPL, 2019

[10] Yu Feng, Ruben Martins, Yuepeng Wang, Isil Dillig, Thomas W. Reps, Component-based synthesis for complex APIs, [ACM SIGPLAN Notices], 2017

基于逻辑规则的代码生成

[11] Z. Manna and R. Waldinger, "Synthesis: Dreams → Programs," in IEEE Transactions on Software Engineering, vol. SE-5, no. 4, pp. 294-328, July 1979, doi: 10.1109/TSE.1979.234198.

[12] Bernd Finkbeiner and Sven Schewe, Bounded synthesis, in Int J Softw Tools Technol Transfer, (2013), 15:519–539, DOI: 10.1007/s10009-012-0228-z

[13] Peter Faymonville, Bernd Finkbeiner, and Leander Tentrup, BoSy: An Experimentation Framework for Bounded Synthesis,CAV 2017

The above is the detailed content of The smart EDA wave is coming, how does ChatGPT help design chips?. For more information, please follow other related articles on the PHP Chinese website!