VSCodeWie konfiguriere ich die Verilog-Umgebung? Der folgende Artikel empfiehlt drei Plug-Ins, damit VSCode reibungslos Verilog schreiben kann. Die drei Plug-Ins können Code-Eingabeaufforderungen + automatische Instanziierung + Formatierung realisieren.

【Empfohlenes Lernen: vscode-Tutorial, Programmiervideo】

Erreichbare Funktionen:

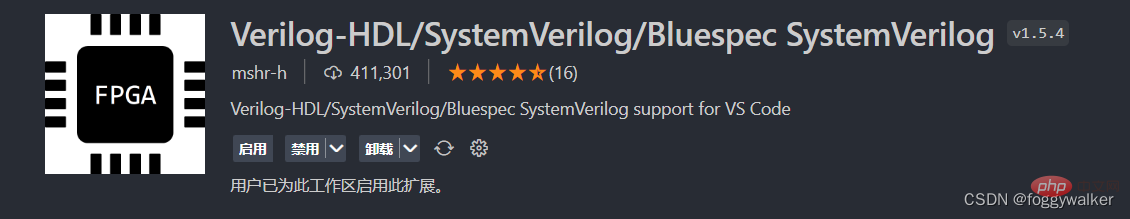

Plug-in-Konfiguration

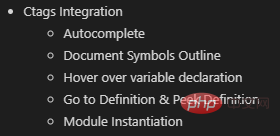

Wie auf der Begrüßungsseite des Verilog HDL/SystemVerilog-Plug-ins erläutert, wird die Ctags-Funktion unterstützt:

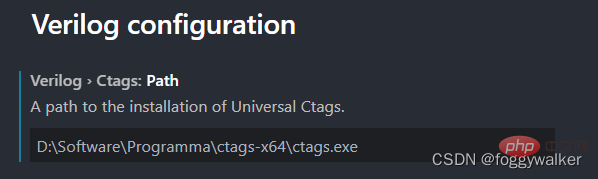

Konfigurationsschritte:

Laden Sie die neueste Version von ctags herunter. Einige Funktionen der alten Version sind nicht vollständig genug. Windows kann die x64-Version auswählen.

Legen Sie den Pfad von ctags.exe zur Systemumgebung fest Variable;

Plug-in-Einstellungen Konfigurieren Sie den Ctags-Pfad;

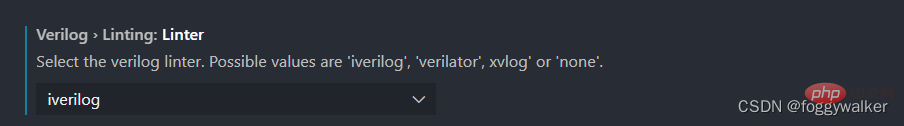

iverilog

modelsim

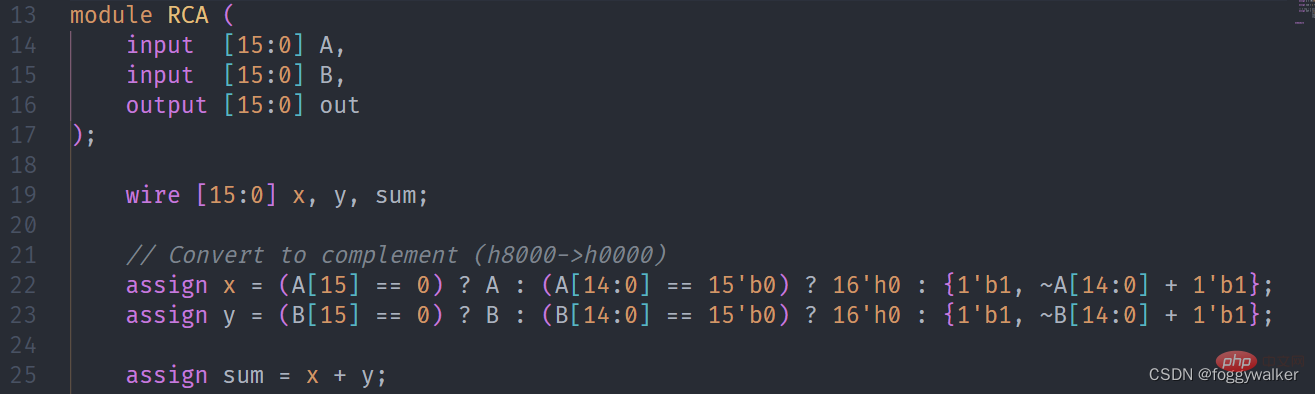

Unterstützt Syntaxhervorhebung wie Verilog und SV.

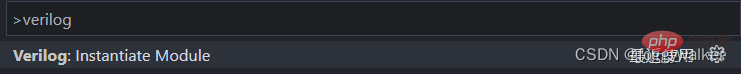

Umschalt+Strg+P Eingabe Verilog, Sie können das Modul direkt automatisch instanziieren.

Platzieren Sie die Maus auf dem Signal und im schwebenden Feld wird eine Aussage angezeigt. Strg + Linksklick, klicken Sie auf den Signalnamen, um automatisch zur Deklaration zu springen. Platzieren Sie den Cursor auf dem Signal, klicken Sie mit der rechten Maustaste und wählen Sie „Definition anzeigen“ (die Tastenkombinationen können Sie hier selbst festlegen). Es ist sehr praktisch, die Deklaration zu ändern, ohne hin und her springen zu müssen .

Erreichbare Funktionen:

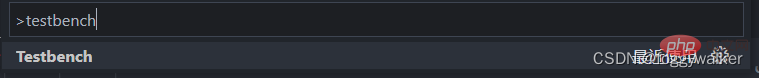

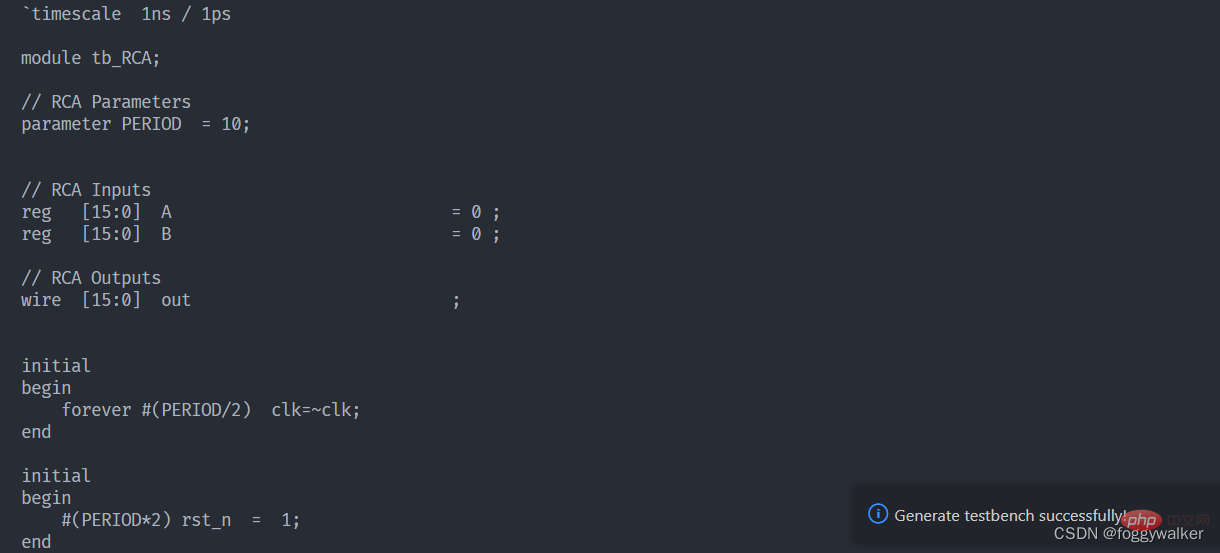

Testbench automatisch generieren

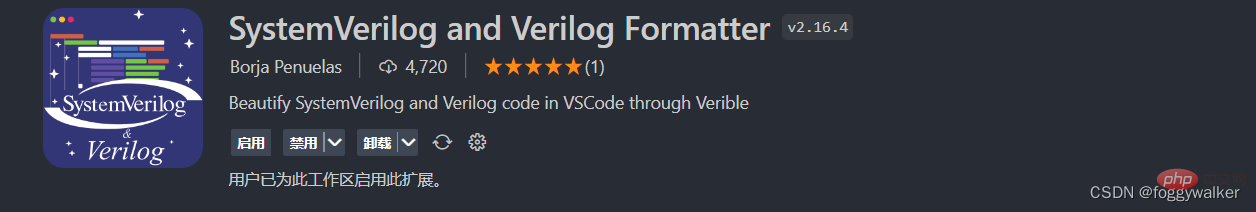

SystemVerilog und Verilog Formatter

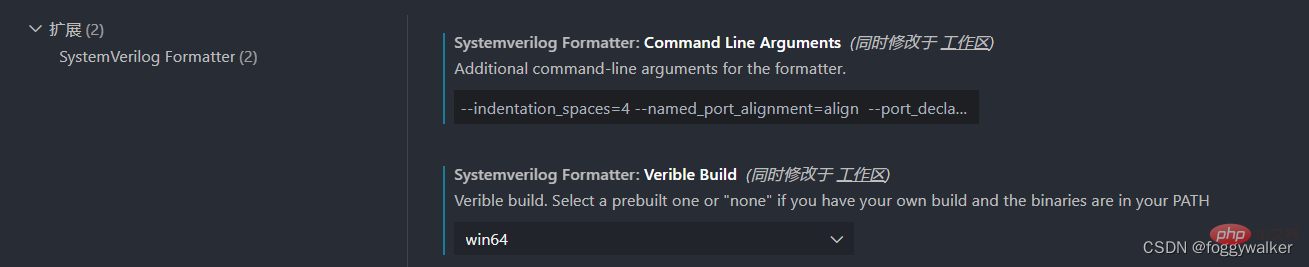

--line_break_penalty (Zur Lösung hinzugefügte Strafe für jeden eingeführten Zeilenumbruch.); Standardwert: 2; --verilog_trace_parser (Trace verilog parser); Standard: false; 插件Die Funktion „SystemverilogFormatter.veribleBuild“ für „Win64“ und „SystemverilogFormatter.commandLineArguments“ ist für die Verwendung in Windows geeignet数,下面放上我自己用的参数,可以实现大部分常用代码段实现对齐。 Funktionen können realisiert werden : Verwendung: Bazel- bin/verilog/tools/formatter/verible-verilog-format [options]

Funktionen können realisiert werden : Verwendung: Bazel- bin/verilog/tools/formatter/verible-verilog-format [options]

--over_column_limit_penalty (Zur Strafminimierung stellt dies den grundlegenden Strafwert für die Überschreitung des Spaltenlimits dar. Für jedes Zeichen über diesem Limit wird eine zusätzliche Strafe von 1 erhoben.) Standard: 100;

--wrap_spaces (Jede Umbruchebene fügt so viele Leerzeichen hinzu. Dies gilt, wenn das erste Element nach einem offenen Gruppenabschnitt umbrochen wird. Andernfalls wird die Einrückungsebene auf die Spaltenposition der offenen Gruppe festgelegt

Operator.); Standard: 4;

Flags from external/com_google_absl/absl/flags/parse.cc:

--flagfile (durch Kommas getrennte Liste von Dateien, aus denen Flags geladen werden sollen); Standard: ;

--fromenv (durch Kommas getrennte Liste von Flags, die aus der Umgebung gesetzt werden sollen [verwenden Sie

'export FLAGS_flag1=value']); Standard: ;

--tryfromenv (durch Kommas getrennte Liste von Flags, die aus der Umgebung gesetzt werden sollen, falls vorhanden); Standard: ;

--undefok (durch Kommas getrennte Liste von Flag-Namen, die in der Befehlszeile angegeben werden dürfen, auch wenn das Programm kein Flag mit diesem Namen definiert); Standard: ;

Flags von verilog/formatting/format_style_init.cc:

--assignment_statement_alignment (Formatieren Sie verschiedene Zuweisungen:

{align,flush-left,preserve,infer}); Standard: infer;

--case_items_alignment (Fallelemente formatieren:

{align,flush-left,preserve,infer}); Standard: infer;

--class_member_variable_alignment (Klassenmitgliedsvariablen formatieren:

{align,flush-left,preserve,infer}); Standard: infer;

--compact_indexing_and_selections (Verwenden Sie kompakte Binärausdrücke innerhalb von

Indexierungs-/Bitauswahloperatoren); Standard: true;

--distribution_items_alignment (Verteilungselemente ausrichten:

{align,flush-left,preserve,infer}); Standard: infer;

--enum_assignment_statement_alignment (Formatzuweisungen mit Aufzählungen:

{align,flush-left,preserve,infer}); Standard: infer;

--expand_coverpoints (Wenn wahr, werden Coverpoints immer erweitert.); Standard: false;

--formal_parameters_alignment (Formale Parameter formatieren:

{align,flush-left,preserve,infer}); Standard: infer;

--formal_parameters_indentation (Formale Parameter einrücken: {indent,wrap});

Standard: wrap;

--module_net_variable_alignment (Netz-/Variablendeklarationen formatieren:

{align,flush-left,preserve,infer}); Standard: infer;

--named_parameter_alignment (Format benannter tatsächlicher Parameter:

{align,flush-left,preserve,infer}); Standard: infer;

--named_parameter_indentation (Benannte Parameterzuweisungen einrücken:

{indent,wrap}); Standard: wrap;

--named_port_alignment (Formatieren Sie benannte Portverbindungen:

{align,flush-left,preserve,infer}); Standard: infer;

--named_port_indentation (Benannte Portverbindungen einrücken: {indent,wrap});

Standard: wrap;

--port_declarations_alignment (Portdeklarationen formatieren:

{align,flush-left,preserve,infer}); default: infer;

--port_declarations_indentation (Portdeklarationen einrücken: {indent,wrap});

default: wrap;

--port_declarations_right_align_packed_dimensions (Wenn wahr, werden gepackte

Dimensionen in Kontexten mit aktivierter Ausrichtung rechtsbündig ausgerichtet.);

Standard: false;

--port_declarations_right_align_unpacked_dimensions (Wenn wahr, werden entpackte Dimensionen in Kontexten mit aktivierter Ausrichtung rechtsbündig ausgerichtet.);

Standard: false;

--struct_union_members_alignment (Struktur-/Union-Mitglieder formatieren:

{align,flush- left,preserve,infer}); Standard: infer;

--try_wrap_long_lines (Wenn wahr, lassen Sie den Formatierer versuchen, Zeilenumbruchentscheidungen dort zu optimieren, wo ein Umbruch erforderlich ist, andernfalls lassen Sie sie unformatiert.

Dies ist eine kurzfristige Maßnahme, um das Risiko von Schäden zu verringern.); Standard: false;

Flags von verilog/tools/formatter/verilog_format.cc:

--failsafe_success (Wenn wahr, immer mit Status 0 beenden, auch wenn

Eingabefehler oder interne Fehler aufgetreten sind. Unter allen Fehlerbedingungen ist immer der Originaltext

vorhanden beibehalten. Dies ist nützlich bei der Bereitstellung von Diensten, bei denen ausfallsicheres Verhalten als Erfolg angesehen werden sollte.); Standard: true;

--inplace (Wenn wahr, überschreiben Sie die Eingabedatei bei erfolgreichen Bedingungen.);

Standard: false;

--lines (Spezifische Zeilen zum Formatieren, 1-basiert, durch Kommas getrennt, einschließlich N-M-Bereiche, N ist die Abkürzung für N-N. Standardmäßig sind alle Zeilen für die Formatierung aktiviert (wiederholbar, kumulativ). Standard: ;

--max_search_states (Begrenzt die Anzahl der Suchzustände, die während der Zeilenumbruchoptimierung untersucht werden.); Standard: 100000;

--show_equally_optimal_wrappings (Wenn wahr, wird gedruckt, wenn mehrere optimale

Lösungen gefunden werden (stderr), aber weiterhin normal funktionieren.);

Standard: false;

--show_inter_token_info (Wenn wahr, zusammen mit show_token_partition_tree,

Fügen Sie Informationen zwischen Token wie Abstand und Unterbrechungsstrafen hinzu.);

Standard: false;

--show_largest_token_partitions (Wenn > 0, Token-Partitionierung drucken und dann

beenden, ohne die Ausgabe zu formatieren.); Standard: 0;

--show_token_partition_tree (Wenn wahr, wird die Diagnose nach der Token-Partitionierung ausgegeben

und dann beendet, ohne die Ausgabe zu formatieren.); Standard: false;

--stdin_name (Wenn „-“ zum Lesen aus stdin verwendet wird, ergibt dies einen alternativen

Namen für Diagnosezwecke. Andernfalls wird dieser ignoriert.);

default: "

--verbose (Seien Sie ausführlicher.); Standard: false;

--verify_convergence (Wenn true und keine inkrementelle Formatierung mit --lines, stellen Sie sicher, dass die Neuformatierung der formatierten Ausgabe keine weiteren Änderungen mit sich bringt, d. h. die Formatierung ist konvergent.); Standard: true;

Versuchen Sie --helpfull, um eine Liste aller Flags zu erhalten, oder --help=substring zeigt Hilfe für

Flags an, die einen angegebenen Teilstring entweder im Namen, in der Beschreibung oder im Pfad enthalten.

--indentation_spaces=4 --named_port_alignment=align --ort_declarations_alignment=align --module_net_variable_alignment=align

和vscode内置格式化一样, drücken Sie Umschalt+Strg+F式化文件,ctrl+k可以格式化选定内容.

值得注意的是,由于这个插件也是在完善中,还是存在部分问题的.

比如,存在

语法问题,或者不能识别语法的时候,格式化会使用不了.这里我将最后一个端口加上“, „就不能格式化了“.础教程!

Das obige ist der detaillierte Inhalt vonWie konfiguriere ich die Verilog-Umgebung in VSCode? Code-Eingabeaufforderungen + automatische Instanziierung + Formatierungs-Plug-In-Freigabe. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

vscode

vscode

So führen Sie Code mit vscode aus

So führen Sie Code mit vscode aus

Einführung in das von vscode verwendete Framework

Einführung in das von vscode verwendete Framework

Welche Sprache wird im Allgemeinen zum Schreiben von vscode verwendet?

Welche Sprache wird im Allgemeinen zum Schreiben von vscode verwendet?

In welcher Sprache kann vscode geschrieben werden?

In welcher Sprache kann vscode geschrieben werden?

vscode Chinesische Einstellungsmethode

vscode Chinesische Einstellungsmethode

Einführung in die Verwendung von vscode

Einführung in die Verwendung von vscode

Der Unterschied zwischen vscode und Visual Studio

Der Unterschied zwischen vscode und Visual Studio