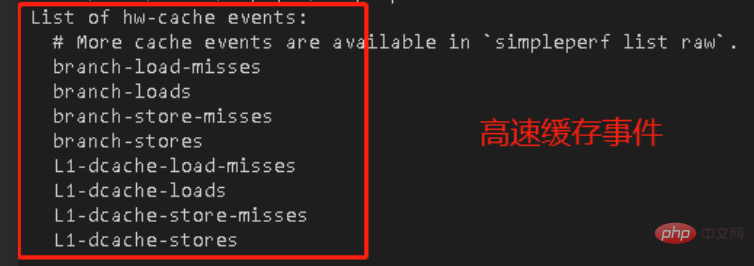

Thing sebenarnya seperti ini. Saya melihat maklumat berikut :

Tugas saya ialah menjadikan peristiwa cache ini dikira secara normal, tetapi yang penting, saya tidak tahu apa maksud misses、loads ini sama sekali.

Saya hanya tahu bahawa kedua-duanya adalah cache, tetapi nama ini sangat serupa, apakah perbezaannya?

Atas sebab ini, saya merasakan bahawa saya perlu belajar tentang cache, dan pemahaman saya tentang cache, prestasi, dsb. bermula dari ini.

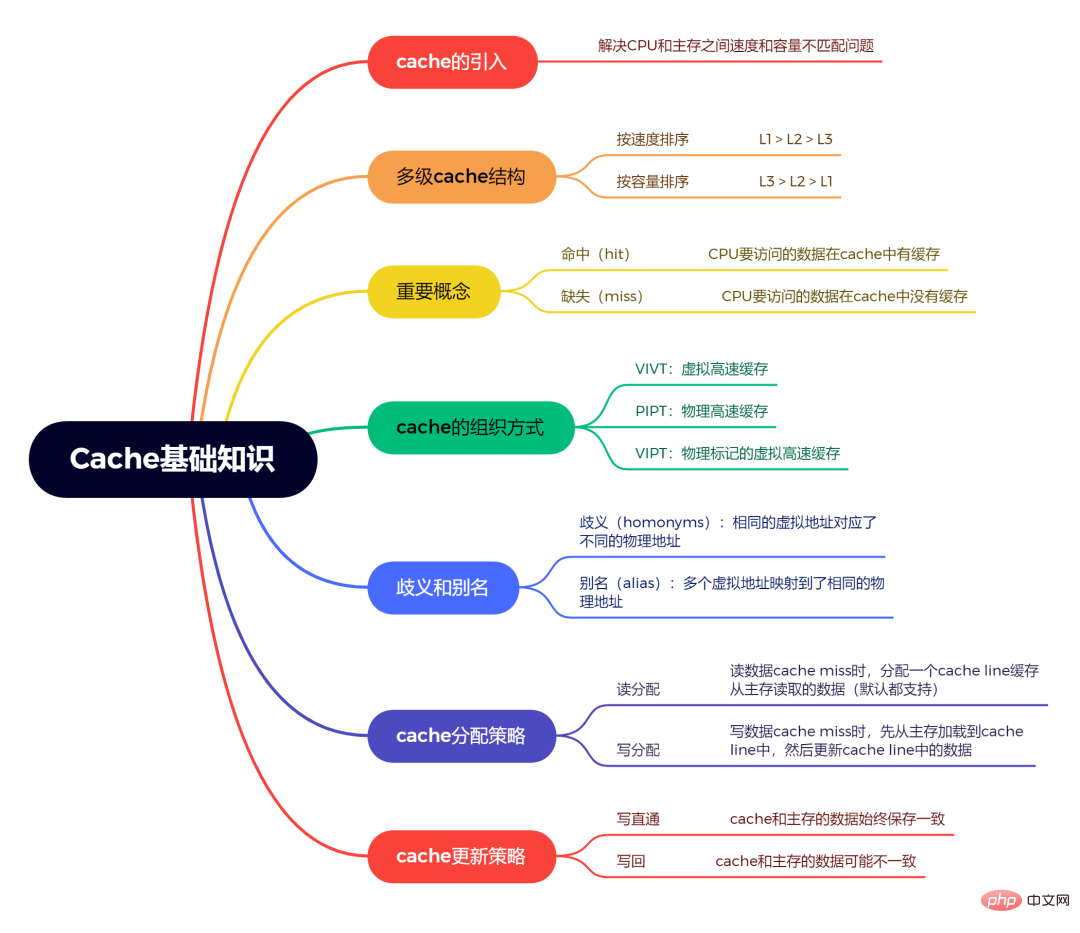

Berikut ialah beberapa pengetahuan konsep asas yang saya rumuskan semasa saya mempelajari cache, saya percaya ia akan membantu orang yang tidak memahami lapisan atau cache yang mendasari.

Pada asasnya, saya akan membimbing semua orang dalam bentuk soalan dan jawapan, kerana saya pernah melaluinya dengan banyak soalan.

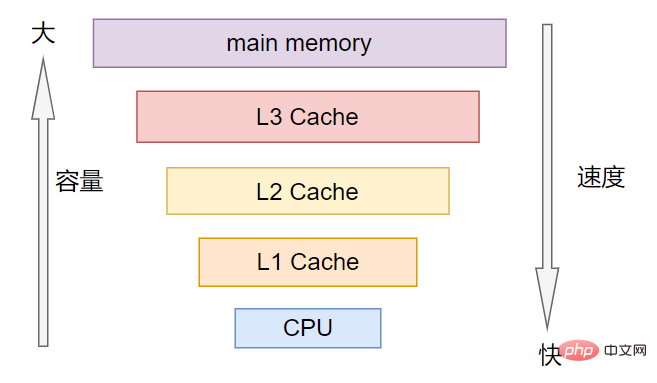

Pertama sekali, kita perlu tahu bahawa CPU tidak mengakses memori secara langsung, tetapi perlu melalui Cache terlebih dahulu.

Punca: Data dalam CPU disimpan dalam daftar Kepantasan mengakses daftar adalah sangat cepat, tetapi kapasiti daftar adalah kecil. Kapasiti memori adalah besar, tetapi kelajuannya perlahan. Untuk menyelesaikan masalah kelajuan dan kapasiti antara CPU dan memori, Cache diperkenalkan.

Cache terletak di antara CPU dan memori utama Apabila CPU mengakses memori utama, ia mula-mula mengakses Cache untuk melihat jika terdapat data sedemikian dalam Cache mengembalikannya ke CPU jika tiada data dalam Cache , dan kemudian mengakses memori utama.

.

Dalam urutan kelajuan, pesanannya ialah L1>L2>L3.

L1 paling hampir dengan CPU dan L3 paling hampir dengan ingatan utama.

Biasanya L1 dibahagikan kepada cache arahan (ICache) dan cache data (<code style="font-size: 14px;padding: 2px 4px;border-radius: 4px;margin-right: 2px;margin-left: 2px;background-color: rgba(27, 31, 35, 0.05);font-family: " operator mono consolas monaco menlo monospace break-all rgb>DCache ), dan cache L1 adalah peribadi kepada CPU, dan setiap CPU mempunyai cache L1.

ICache)和data cache(DCache),并且L1 cache是cpu私有的,每个cpu都有一个L1 cache。

命中:CPU要访问的数据在cache中有缓存,称为“命中”,即cache hit

缺失:CPU要访问的数据在cache中没有缓存,称为“缺失”,即cache miss

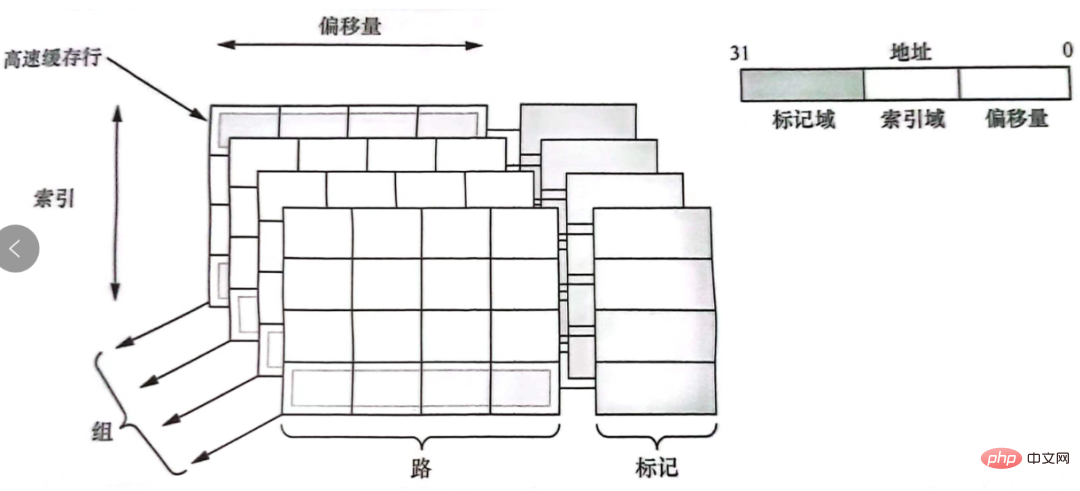

cache hit🎜🎜🎜missing🎜: Data yang akan diakses oleh CPU tidak dicache dalam cache, iaitu dipanggil "hilang", iaitu, cache miss🎜garis cache: tinggi kelajuan Cache line, membahagikan cache kepada banyak blok yang sama, dan saiz setiap blok dipanggil baris cache. cache line:高速缓存行,将cache平均分成相等的很多块,每一个块大小称之为cache line。

cache line也是cache和主存之间数据传输的最小单位.

当CPU试图load一个字节数据的时候,如果cache缺失,那么cache控制器会从主存中一次性的load cache line大小的数据到cache中。例如,cache line大小是8字节。CPU即使读取一个byte,在cache缺失后,cache会从主存中load 8字节填充整个cache line。

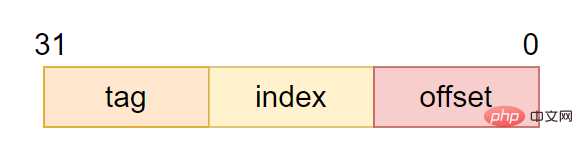

CPU访问cache时的地址编码,通常由tag、index和offset三部分组成:

tag(标记域):用于判断cache line缓存的数据的地址是否和处理器寻址地址一致。- index(索引域):用于索引和查找地址在高速缓存中的哪一行

offsetgarisan cache juga merupakan unit terkecil pemindahan data antara cache dan memori utama Apabila CPU cuba memuatkan satu bait data, jika cache tiada, pengawal cache akan memuatkan data bersaiz baris cache daripada memori utama ke dalam cache pada satu masa. Sebagai contoh, saiz baris cache ialah 8 bait. Walaupun CPU membaca satu bait, selepas cache hilang, cache akan memuatkan 8 bait daripada memori utama untuk mengisi keseluruhan baris cache.

tag(medan tag)🎜: digunakan untuk menentukan baris cache cache Sama ada alamat data konsisten dengan alamat alamat pemproses. 🎜🎜🎜🎜- index (Medan indeks) 🎜: Digunakan untuk mengindeks dan mencari baris mana dalam cache alamat berada dalam 🎜offset🎜 (offset) 🎜: Offset dalam talian cache. Kandungan baris cache boleh ditangani dengan perkataan atau bait 🎜🎜🎜🎜Hubungan antara baris cache dan tag, indeks, offset, dan lain-lain adalah seperti yang ditunjukkan dalam rajah: 🎜

Kita tahu bahawa CPU mengakses memori bukan secara langsung, tetapi CPU mengeluarkan alamat maya, yang kemudiannya ditukar menjadi alamat fizikal oleh MMU, dan kemudian data diambil dari memori mengikut alamat fizikal . Jadi adakah cache mengakses alamat maya atau alamat fizikal?

J: Tidak semestinya. Ia boleh sama ada alamat maya, alamat fizikal, atau gabungan alamat maya dan fizikal.

Oleh kerana cache mempunyai pelbagai kaedah organisasi dalam reka bentuk perkakasan:

VIVTCache mayaVIVT虚拟高速缓存:虚拟地址的index,虚拟地址的tag。PIPT物理高速缓存:物理地址的index,物理地址的tag。VIPT物理标记的虚拟高速缓存:虚拟地址的index,物理地址的tag。歧义(homonyms: indeks alamat maya, teg alamat maya.

PIPT code><strong style="color: black;">Cache fizikal 🎜: indeks alamat fizikal, teg alamat fizikal. </strong>VIPT code><strong style="color: black;">Cache maya teg fizikal 🎜: indeks alamat maya, teg alamat fizikal. </strong>

homonim )🎜: Alamat maya yang sama sepadan dengan alamat fizikal yang berbeza🎜Alias (alias)alias):多个虚拟地址映射到了相同的物理地址(多个虚拟地址被称为别名)。

例如上述VIVT方式就会存在别名问题,那VIVT、PIPT和VIPT那个方式更好呢?

PIPT其实是比较理想的,因为index和tag都使用了物理地址,软件层面不需要任何维护就能避免歧义和别名问题。

VIPT的tag使用了物理地址,所以不存在歧义问题,但index是虚拟地址,所以可能也存在别名问题。

而VIVT : banyak alamat maya dipetakan ke alamat fizikal yang sama (berbilang alamat maya dipanggil alias). Sebagai contoh, kaedah VIVT yang dinyatakan di atas akan mempunyai masalah alias yang lebih baik, VIVT, PIPT atau VIPT?

PIPT sebenarnya lebih ideal. Kerana kedua-dua indeks dan teg menggunakan alamat fizikal, Tiada penyelenggaraan diperlukan pada peringkat perisian untuk mengelakkan kekaburan dan masalah alias.

DanVIPTteg menggunakan fizik alamat, jadi tidak ada masalah kekaburan, tetapi indeks adalah alamat maya, jadi mungkin juga ada masalah alias.

VIVT cara, Penyusunan cache, serta isu kesamaran dan alias, adalah kandungan yang agak besar. Di sini anda hanya perlu tahu bahawa alamat yang diakses oleh cache boleh menjadi alamat maya, alamat fizikal, atau gabungan alamat maya dan alamat fizikal. Dan kaedah organisasi yang berbeza akan mempunyai masalah kekaburan dan alias.

🎜🎜🎜7. Strategi peruntukan cache? 🎜🎜 🎜🎜🎜🎜 merujuk kepada cara cache diperuntukkan apabila kehilangan cache berlaku. 🎜🎜Baca peruntukan: Apabila CPUbaca data, berlakucache tiada, ini Dalam semua kes, garis cacheCache daripada Data dibaca dari ingatan utama. CPU读数据时,发生cache缺失,这种情况下都会分配一个cache line缓存从主存读取的数据。默认情况下,cache都支持读分配。

写分配:当CPU写数据发生cache缺失时,才会考虑写分配策略。当我们不支持写分配的情况下,写指令只会更新主存数据,然后就结束了。当支持写分配的时候,我们首先从主存中加载数据到cache line中(相当于先做个读分配动作),然后会更新cache lineSecara lalai, cache semua sokongan bacaan mengedarkan .

baris cache (bersamaan dengan melakukan peruntukan baca dahulu), dan kemudian kemas kini data dalam baris cache.

8. Strategi kemas kini cache?

merujuk kepada cara operasi tulis harus mengemas kini data apabila cache mencecah.

🎜Tulis laluan🎜: Apabila CPU melaksanakan arahan kedai dan cache mencecah, kami mengemas kini data dalam cache dan mengemas kini data dalam memori utama. 🎜Data dalam cache dan ingatan utama sentiasa konsisten🎜. 🎜Tulis kembali : dikemas kini apabila CPU执行store指令并在cache命中时,我们只更新cache中的数据。并且每个cache line中会有一个bit位记录数据是否被修改过,称之为dirty bit。我们会将dirty bit置位。主存中的数据只会在cache line被替换或者显示的clean beroperasi. Oleh itu, data dalam memori utama mungkin merupakan data yang tidak diubah suai, manakala data yang diubah suai terletak dalam cache . Data dalam cache dan ingatan utama mungkin tidak konsisten.

Mengenai cache, serta TLB, MESI, model ketekalan memori, dll., ia adalah sesuatu yang memerlukan pemendakan dan ringkasan untuk benar-benar menguasai.

Tetapi ramai orang mungkin tidak menggunakannya Hanya apabila ia berkaitan dengan isu prestasi dan apabila anda perlu meningkatkan kadar hit cache, anda akan tahu kepentingan pengetahuan ini.

Mengenai pengetahuan yang dibincangkan dalam artikel ini, saya merumuskan peta minda tentang pengetahuan asas cache:

Atas ialah kandungan terperinci Selepas menyertai syarikat itu, saya faham apa itu Cache. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Apakah senario aplikasi mod tunggal PHP?

Apakah senario aplikasi mod tunggal PHP?

Perbezaan antara mac air dan pro

Perbezaan antara mac air dan pro

Apakah fail .Xauthority?

Apakah fail .Xauthority?

nombor python kepada rentetan

nombor python kepada rentetan

Bagaimana untuk berkongsi pencetak antara dua komputer

Bagaimana untuk berkongsi pencetak antara dua komputer

Bagaimana untuk menyelesaikan gesaan komputer tentang memori yang tidak mencukupi

Bagaimana untuk menyelesaikan gesaan komputer tentang memori yang tidak mencukupi

Bagaimana untuk membaiki winntbbu.dll hilang

Bagaimana untuk membaiki winntbbu.dll hilang

Bagaimana untuk menyediakan memori maya

Bagaimana untuk menyediakan memori maya