VSCodeBagaimana untuk mengkonfigurasi persekitaran verilog? Artikel berikut mengesyorkan tiga pemalam untuk semua orang membenarkan VSCode menulis verilog dengan lancar Ketiga-tiga pemalam itu boleh merealisasikan gesaan kod, instantiasi automatik dan pemformatan.

[Pembelajaran yang disyorkan: Tutorial vskod, Video pengaturcaraan]

Fungsi yang tersedia:

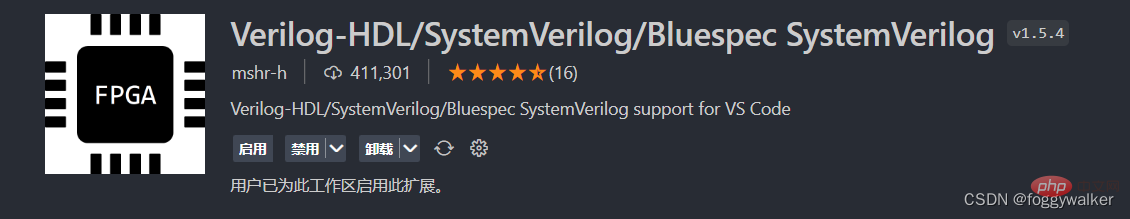

Konfigurasi pemalam

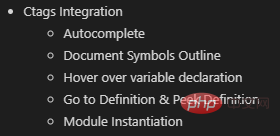

Seperti yang diterangkan pada halaman alu-aluan pemalam Verilog HDL/SystemVerilog, fungsi Ctags disokong:

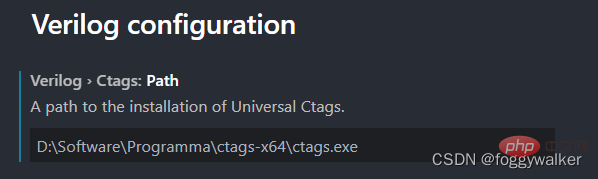

Langkah konfigurasi:

Muat turun versi terkini ctags, sesetengah fungsi versi lama tidak cukup lengkap; Windows boleh memilih versi x64;

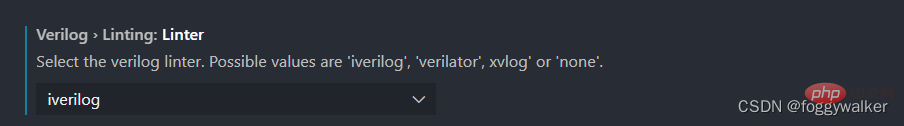

Tukar ctags.exe Tetapkan laluan kepada pembolehubah persekitaran sistem; > Mulakan semula VSCode;Anda boleh memilih penyusun berbeza

iverilog

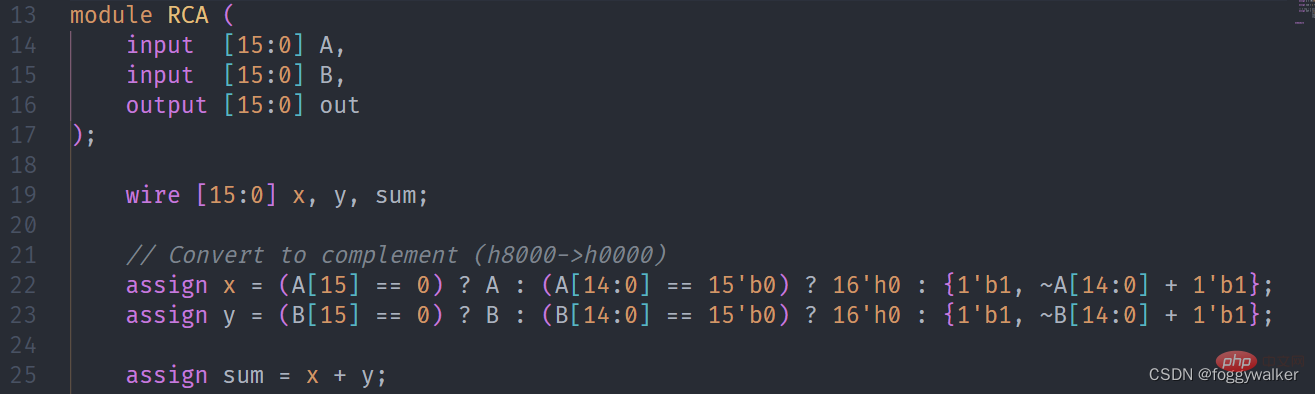

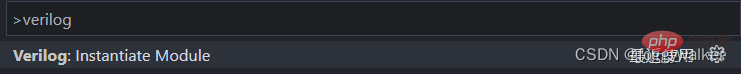

anjakan ctrl p input verilog, anda boleh terus instantiate modul secara automatik. Letakkan tetikus pada isyarat dan kenyataan akan dipaparkan dalam kotak terapung. Ctrl klik kiri dan klik pada nama isyarat untuk melompat ke pengisytiharan secara automatik. Letakkan kursor pada isyarat, klik kanan dan pilih Lihat Definisi (kekunci pintasan boleh diikat sendiri Anda boleh mengembangkan kod pada pengisytiharan di sini. Sangat mudah untuk mengubah suai perisytiharan tanpa perlu melompat ke sana ke mari .

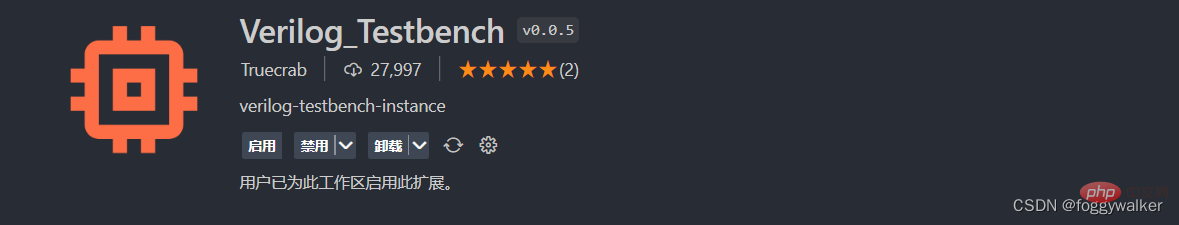

Verilog_Testbench

Fungsi yang tersedia:

Fungsi yang tersedia:

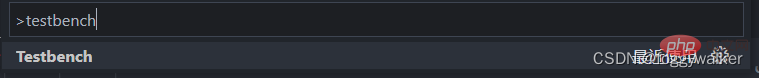

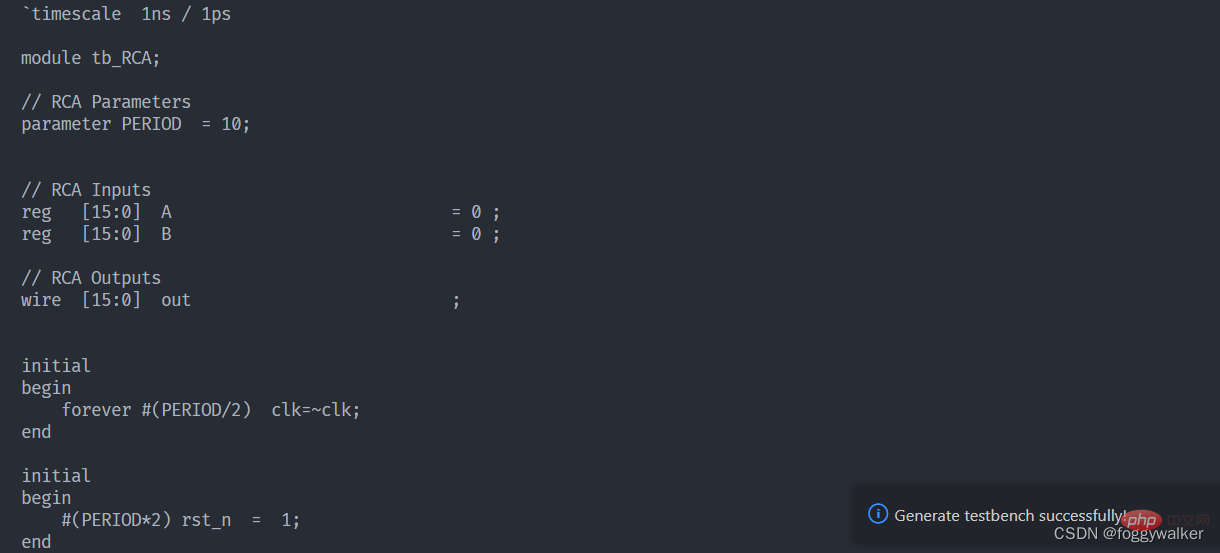

Menjana testbench secara automatik

shift ctrl p input testbench, anda boleh terus menjana tb. Kemudian salinnya di terminal.

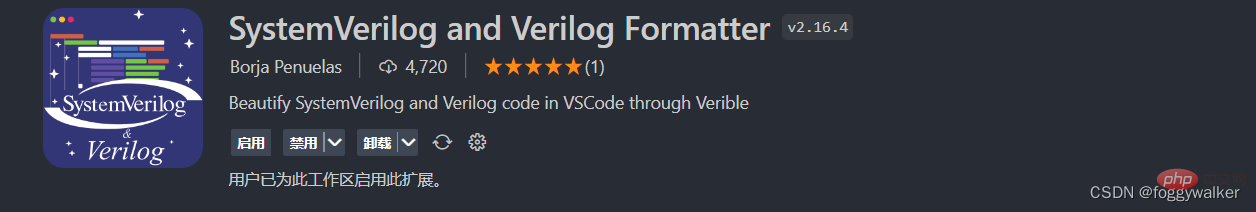

Alat ini dilancarkan oleh Google dan menyokong Verilog dan System Verilog ,

Kesannya sangat baik, dan ia juga menyokong pelbagai parameter pemformatan tersuai. Secara peribadi, saya fikir ia lebih mudah digunakan daripada format verilog.

Format fail secara automatikFormatkan kandungan yang dipilih secara automatik

Format fail secara automatikFormatkan kandungan yang dipilih secara automatik

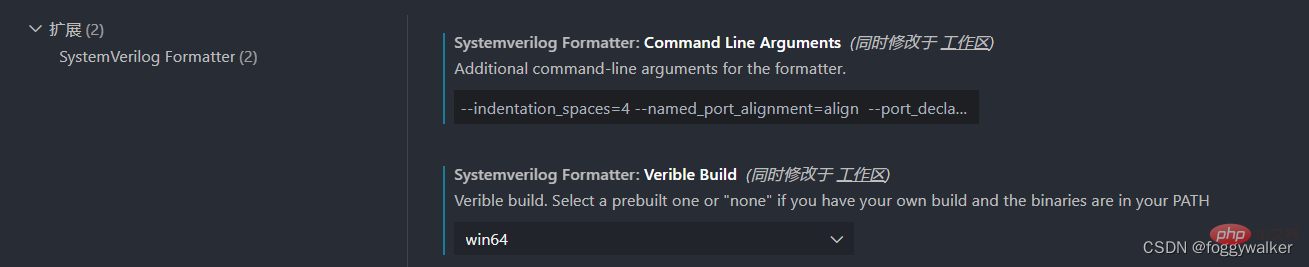

Format tersuai

Jadual tetapan parameter tersuai Bendera daripada common/formatting/basic_format_style_init.cc:

--column_limit (Had panjang baris sasaran untuk kekal di bawah semasa memformat.);

lalai: 100;

--tambahan aras lekukan ini banyak ruang.);

lalai: 2;

--line_break_penalty (Penalti ditambahkan pada penyelesaian untuk setiap baris yang diperkenalkan

break.); lalai: 2;

--over_column_limit_penalty (Untuk meminimumkan penalti, ini mewakili

nilai penalti garis dasar melebihi had lajur. Penalti tambahan

daripada 1 ditanggung untuk setiap aksara melebihi had ini); lalai: 100;

--wrap_spaces (Setiap tahap balut menambah banyak ruang ini. Ini terpakai apabila

elemen pertama selepas bahagian kumpulan terbuka dibalut. Jika tidak, tahap lekukan

ditetapkan pada lajur kedudukan pengendali kumpulan terbuka

.); lalai: 4;

Bendera daripada external/com_google_absl/absl/flags/parse.cc:

--flagfile (senarai fail yang dipisahkan koma untuk memuatkan bendera); lalai: ;

--fromenv (senarai bendera yang dipisahkan koma untuk ditetapkan daripada persekitaran [gunakan

'eksport FLAGS_flag1=value']); lalai: ;

--tryfromenv (senarai bendera yang dipisahkan koma untuk cuba ditetapkan daripada persekitaran

jika ada); lalai: ;

--undefok (senarai nama bendera yang dipisahkan koma yang boleh ditentukan pada

baris arahan walaupun program tidak mentakrifkan bendera dengan nama itu

); lalai: ;

Benderakan daripada verilog/formatting/format_style_init.cc:

--assignment_statement_alignment (Formatkan pelbagai tugasan:

{align,flush-left,preserve,infer}); lalai: infer;

--case_items_alignment (Formatkan item kes:

{align,flush-left,preserve,infer}); lalai: infer;

--class_member_variable_alignment (Formatkan pembolehubah ahli kelas:

{align,flush-left,preserve,infer}); lalai: infer;

--compact_indexing_and_selections (Gunakan ungkapan binari padat di dalam

pengendali pengindeksan / pemilihan bit); lalai: benar;

--distribution_items_alignment (Item pengedaran Algh:

{align,flush-left,preserve,infer}); lalai: infer;

--enum_assignment_statement_alignment (Formatkan tugasan dengan enum:

{align,flush-left,preserve,infer}); lalai: infer;

--expand_coverpoints (Jika benar, sentiasa kembangkan coverpoints.); lalai: palsu;

--formal_parameters_alignment (Formatkan parameter formal:

{align,flush-left,preserve,infer}); lalai: infer;

--formal_parameters_indentation (Indent parameter formal: {indent,wrap});

lalai: wrap;

--module_net_variable_alignment (Format net/pengisytiharan pembolehubah: kiri, pelihara, simpulkan}); lalai: infer;

--named_parameter_alignment (Format dinamakan parameter sebenar:

{align,flush-left,preserve,infer}); lalai: infer;

--named_parameter_indentation (Indent name parameter assignments:

{indent,wrap}); lalai: bungkus;

--named_port_alignment (Format bernama sambungan port:

{align,flush-left,preserve,infer}); lalai: infer;

--named_port_indentation (Indent bernama sambungan port: {indent,wrap});

lalai: wrap;

--port_declarations_alignment (Formatkan pengisytiharan port:

{align ,pelihara, simpulkan}); lalai: infer;

--port_declarations_indentation (Indent port declarations: {indent,wrap});

lalai: wrap;

--port_declarations_right_align_packed_dimensions (Jika benar, dimasukkan dalam konteks lalai dalam konteks dijajarkan ke kanan.);

lalai: false;

--port_declarations_right_align_unpacked_dimensions (Jika benar, unpacked

dimensi dalam konteks dengan penjajaran didayakan dijajarkan ke kanan. > lalai.); --struct_union_members_alignment (Formatkan struct/anggota kesatuan:

{align,flush-left,preserve,infer}); lalai: infer;

--try_wrap_long_lines (Jika benar, biarkan pemformat cuba mengoptimumkan baris

keputusan pembalut di mana pembalut diperlukan, jika tidak, biarkan mereka tidak diformatkan.

Ini adalah langkah jangka pendek untuk mengurangkan risiko- kemudaratan.); lalai: false;

Bendera daripada verilog/parser/verilog_parser.cc:

--verilog_trace_parser (Jejak verilog parser); lalai: palsu;

Benderakan daripada verilog/tools/formatter/verilog_format.cc:

--failsafe_success (Jika benar, sentiasa keluar dengan status 0, walaupun terdapat

ralat input atau ralat dalaman. Dalam semua ralat syarat, teks

asal sentiasa dikekalkan Ini berguna dalam melaksanakan perkhidmatan di mana

gelagat selamat gagal harus dianggap berjaya.); lalai: benar;

--inplace (Jika benar, tulis ganti fail input pada keadaan yang berjaya.);

lalai: false;

--lines (Barisan khusus untuk diformat, berasaskan 1, dipisahkan koma , termasuk julat N-M

, N adalah singkatan untuk N-N Secara lalai, dibiarkan tidak ditentukan, semua baris

didayakan untuk pemformatan (boleh berulang, terkumpul)); lalai: ;

--max_search_states (Menghadkan bilangan keadaan carian yang diterokai semasa baris

pengoptimuman bungkus.); lalai: 100000;

--show_equally_optimum_wrappings (Jika benar, cetak apabila berbilang penyelesaian optimum

ditemui (stderr), tetapi terus beroperasi seperti biasa.);

lalai: false; sertakan maklumat antara token seperti jarak dan penalti putus.);

lalai: false;

--show_largest_token_partitions (Jika > 0, cetak token kemudian

keluar tanpa memformat output.); lalai: 0;

--show_token_partition_tree (Jika benar, cetak diagnostik selepas token

pembahagian dan kemudian keluar tanpa memformat output.); lalai: palsu;

--stdin_name (Apabila menggunakan '-' untuk membaca daripada stdin, ini memberikan nama alternatif

untuk tujuan diagnostik. Jika tidak, ini diabaikan.);

lalai: "

--verbose (Jadilah lebih bertele-tele.); lalai: false;

--verify_convergence (Jika benar, dan tidak memformat secara berperingkat dengan

--lines, sahkan bahawa memformat semula output yang diformatkan tidak menghasilkan perubahan lagi

, iaitu pemformatan adalah menumpu.); lalai: true;

bendera yang menyertakan subrentetan yang ditentukan sama ada dalam nama, atau perihalan atau

laluan.

插件配置

--indentation_spaces=4 --named_port_alignment=align --ort_declarations_alignment=align --module_net_variable_alignment=align

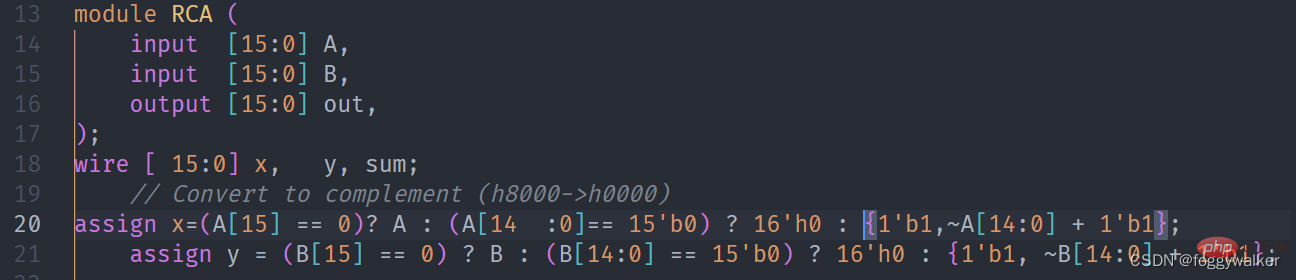

如何使用?如何格式化?

和vscode内置格式化一样,直接shift ctrl,小小可以格式化选定内容。值得注意的是,由于这个插件也是在完善中,还是存在部分问题的。

比如,存在

语法问题,或者不能识别语法的时候,格式化会使用不了。这里我将最后将最后与,"丱后与能格式化了。

更多关于VSCode的相关知识,请访问: vscode基础教程

vscode基础教程

Atas ialah kandungan terperinci Bagaimana untuk mengkonfigurasi persekitaran verilog dalam VSCode? Petua kod, instantiasi automatik, pemformatan perkongsian pemalam. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

vscode

vscode

Bagaimana untuk menjalankan kod dengan vscode

Bagaimana untuk menjalankan kod dengan vscode

Pengenalan kepada rangka kerja yang digunakan oleh vscode

Pengenalan kepada rangka kerja yang digunakan oleh vscode

Bahasa apakah yang biasanya digunakan untuk menulis vscode?

Bahasa apakah yang biasanya digunakan untuk menulis vscode?

Bahasa apa yang boleh ditulis vscode?

Bahasa apa yang boleh ditulis vscode?

vscode kaedah tetapan Cina

vscode kaedah tetapan Cina

Pengenalan kepada penggunaan vscode

Pengenalan kepada penggunaan vscode

Perbezaan antara vscode dan visual studio

Perbezaan antara vscode dan visual studio