5월 26일 보도에 따르면, 국내 언론 더일렉에 따르면 삼성전자는 최근 4F²라는 기술 개발을 전담하는 전문팀을 꾸렸다. DRAM 메모리 셀 구조의 혁신적인 기술입니다. 이 기술은 프로세스 노드를 변경하지 않고도 칩 면적을 최대 30%까지 줄일 수 있습니다.

지난 10년 동안 DRAM 업계는 4F 상용화를 시도해왔습니다. 각형 단위구조 기술은 성공하지 못함. 그러나 이번에 삼성이 꾸린 전문팀은 기존의 문제점을 극복하고 4F² 구조의 연구개발을 추진하기 위해 노력하고 있다.

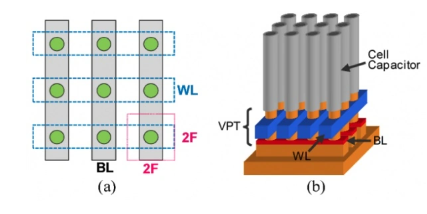

에디터가 아는 한 4F² DRAM 메모리 셀 구조의 설계는 트랜지스터로 구성된 소스(S), 게이트(G) 및 드레인(D)의 전체 시스템을 기반으로 합니다. 드레인(D) 위쪽에는 전하를 저장하는 커패시터가 설치되어 있고, 트랜지스터는 수평으로 배열된 WL 라인과 수직으로 배열된 BL 라인에 연결되어 있다. 그 중 WL 라인은 게이트(G)에 연결되어 트랜지스터의 스위칭을 제어하는 역할을 하고, BL 라인은 소스(S)에 연결되어 데이터 읽기 및 쓰기를 담당합니다.

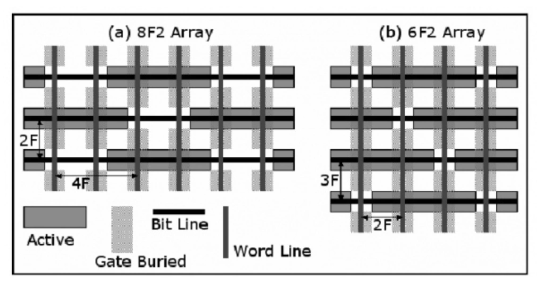

4F² 기술의 가장 큰 장점은 높은 집적도와 칩 공간 절약 능력입니다. 이 기술은 기존 6F² 수준과 비교해 공정 노드 변경 없이 칩 면적을 최대 30%까지 줄일 수 있다. 이는 칩 성능을 개선하고, 더 높은 용량의 메모리를 달성하며, 증가하는 시장 수요를 충족하는 데 큰 의미가 있습니다.

삼성 전문팀은 4F²의 속도를 높이기 위해 계속 노력하겠습니다. DRAM 메모리 셀 구조의 개발 과정. 이 기술이 성공적으로 상용화되면 DRAM 산업에 획기적인 혁신을 가져오고 메모리 기술 발전을 새로운 차원으로 끌어올릴 것으로 기대됩니다. 우리는 이 분야의 최신 발전에 계속해서 주의를 기울일 것입니다.

위 내용은 삼성전자, 4F² DRAM 메모리 셀 구조 기술 개발 전담팀 구성의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!