ZDNet によると、サムスンは将来の Exynos シリーズ SoC に 3D チップレット技術を適用することを積極的に検討中です

情報筋は、「サムスン電子は社内で Exynos に 3D チップレットを適用することを検討している」と説明しました。そうすることで得られるものです」と彼は付け加えた。同氏は、3DチップレットはExynosの生産効率を向上させ、それによって競争力を強化するのに役立つと指摘した。

チップレットは主に、特定の機能を満たし、ダイツーダイの内部相互接続技術を通じて複数のモジュールを実装するダイ (ベアチップ) の一種です。チップは、基礎となる基本チップとともにパッケージ化されてシステム チップを形成し、主流の SoC 設計概念とは大きく異なる新しい形式の IP 再利用を実現します。

現在、主流の SoC システム レベルのシングル チップは、主にフォトリソグラフィーを通じて、さまざまなタイプのコンピューティング タスクを担当する複数のコンピューティング ユニットを同じウェーハ上に製造しています。たとえば、携帯電話の AP チップには、CPU、GPU、DSP、ISP、NPU、モデムなどのさまざまなユニットと、多数のインターフェイス IP

が統合されています。比較的言えば、チップレットはオリジナルです。複雑なSoCチップを設計する際には、まず計算ユニットや機能ユニットに分解し、それぞれのユニットに最適な半導体プロセス技術を選択して個別に製造し、高度なパッケージング技術によって各ユニットを相互接続します。 、最終的にシステムレベルのチップセットに統合およびパッケージ化されます。

チップ製造プロセスが 1 桁のナノメートル (nm) に進化するにつれ、プロセスの難易度や内部構造の複雑さは増加し続けています。製造プロセスが複雑化し、チッププロセス全体の設計コストが大幅に増加することが、チップレットの影響を受ける大きな懸念材料となっています。 チップ製造プロセスがナノメートルレベルに進むにつれて、プロセスの難易度や内部構造の複雑さは増加し続けており、製造プロセスもより複雑になり、チップの全プロセス設計コストが大幅に増加しています。これもチップレットが広く注目を集めている重要な理由です

近年の「ムーアの法則」の減速を背景に、チップレットは業界で大きな期待を寄せられている技術となっており、今後も「経済成長」が続く可能性があります。ムーアの法則の利点」を別の角度から見る

現在、NVIDIA、AMD、Intel などの有名企業が、ハイ パフォーマンス コンピューティング (HPC) システム用の半導体開発にチップ コンポーネントを導入しています。カナダの AI 半導体スタートアップ TenStorent も最近、Samsung のファウンドリを使用して 4nm チップを生産すると発表したことに気づきました

海外メディアもモバイルアプリケーション処理 デバイスは、最先端のファウンドリ技術が必要な分野であり、歩留まりに非常に敏感です。したがって、3D チップセットを使用することで、より安定した生産を実現できます。

さらに、3D パッケージング技術により、チップ全体のパッケージ サイズをさらに縮小し、チップ間の接続性を向上させることができます。帯域幅と効率

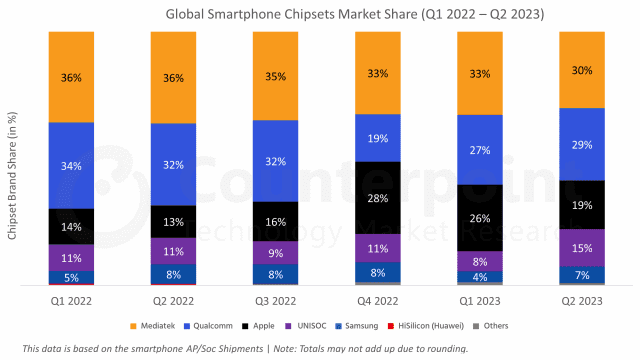

市場調査会社 Counterpoint Research のデータによると、今年第 2 四半期のモバイル AP 市場シェアは売上高で計算され、クアルコムが 40 社を占めました。 %. %、Apple は 33%、MediaTek は 16%、Samsung Electronics は 7% のみを占めています

広告文: この記事には外部ジャンプ リンク (ハイパーリンク、QR コード、パスワードやその他のフォーム)、より多くの情報を提供し、審査時間を節約することを目的としており、結果は参考のみです。このサイトのすべての記事にこの記述が含まれていることにご注意ください

以上がサムスンがExynos SoCで3Dチップレット技術の使用を検討しているというニュースの詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。