過去 10 年間はディープラーニングの「黄金の 10 年」であり、人間の働き方や遊び方を完全に変え、医療、教育、製品デザインなどのさまざまな業界で広く使用されています. コンピューティング ハードウェアの進歩、特に GPU の革新。

ディープ ラーニング テクノロジの実装が成功するかどうかは、3 つの主要な要素に依存します。 1 つ目はアルゴリズムです。ディープ ニューラル ネットワーク、畳み込みニューラル ネットワーク、逆伝播アルゴリズム、確率的勾配降下法などの深層学習アルゴリズムのほとんどは、1980 年代かそれ以前に提案されました。

2 番目はデータセットです。ニューラル ネットワークのトレーニングに使用されるデータ セットは、ニューラル ネットワークが他の手法よりも優れたパフォーマンスを発揮できるように十分な大きさでなければなりません。 Pascal や ImageNet などのビッグ データ セットが利用可能になったのは 21 世紀初頭になってからです。 3つ目はハードウェアです。成熟したハードウェア開発によってのみ、大規模なデータ セットを使用して大規模なニューラル ネットワークをトレーニングするのに必要な時間を妥当な範囲内に制御できます。業界では一般的に、より「合理的な」トレーニング時間は約 2 週間であると考えられています。

現時点で、ディープラーニングの分野で大草原の火が点火されています。アルゴリズムとデータ セットがディープ ラーニングの混合燃料とみなされる場合、GPU はそれらを点火する火花であり、強力な GPU をネットワークのトレーニングに使用できるようになると、ディープ ラーニング テクノロジが実用的になります。

それ以来、ディープラーニングは他のアルゴリズムに取って代わり、画像分類、画像検出、音声認識、自然言語処理、時系列分析などの分野で広く使用されています。囲碁やチェスも見ることができます。ディープラーニングが人間の生活のあらゆる側面に浸透するにつれて、モデルのトレーニングと推論にはますますハードウェアの要求が厳しくなってきています。

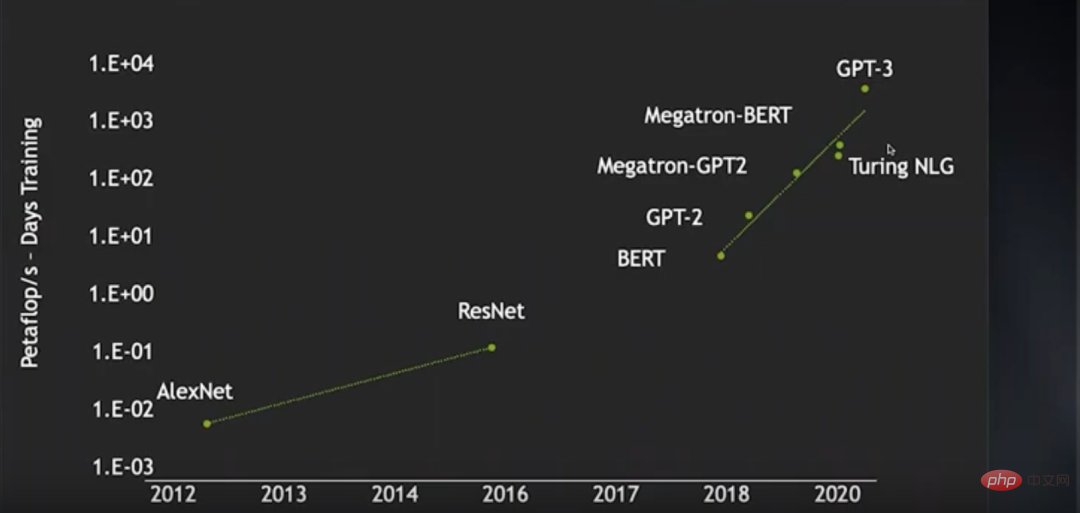

2012 年の AlexNet の出現から 2016 年の ResNet の出現まで、トレーニングは画像ニューラル ネットワークのアルゴリズムの消費電力 (ペタフロップス/s-日) は 2 桁近く増加していますが、2018 年の BERT から近年の GPT-3 まで、トレーニング コンピューティングの消費電力は 4 桁近く増加しています。この期間中、特定のテクノロジーの進歩のおかげで、ニューラル ネットワークのトレーニング効率が大幅に向上し、多くの計算能力が節約されました。そうでなければ、計算能力の消費量の増加はさらに誇張されることになります。

研究者らは、より大規模な教師なし言語データセットを使用して、より大きな言語モデルをトレーニングしたいと考えていました。しかし、すでに 4000 ノードの GPU クラスターを持っていましたが、妥当な範囲内でトレーニングするのは困難でした。処理できる操作は依然として非常に限られています。これは、ディープラーニング技術の開発速度がハードウェアの開発速度に依存することを意味します。

現在、深層学習モデルはますます複雑になっているだけでなく、応用範囲もますます広がっています。したがって、深層学習のパフォーマンスを向上し続ける必要があります。では、ディープ ラーニング ハードウェアはどのようにして改善を続けることができるのでしょうか? NVIDIA のチーフ サイエンティストである Bill Dally は、間違いなくこの質問に答える権威です。H100 GPU のリリース前に、彼は講演でディープ ラーニング ハードウェアの現状をレビューし、ムーアの法則が適用されたときのパフォーマンスの継続的な向上について議論しました。拡張にはいくつかの方向があります。 OneFlow コミュニティがこれをまとめました。

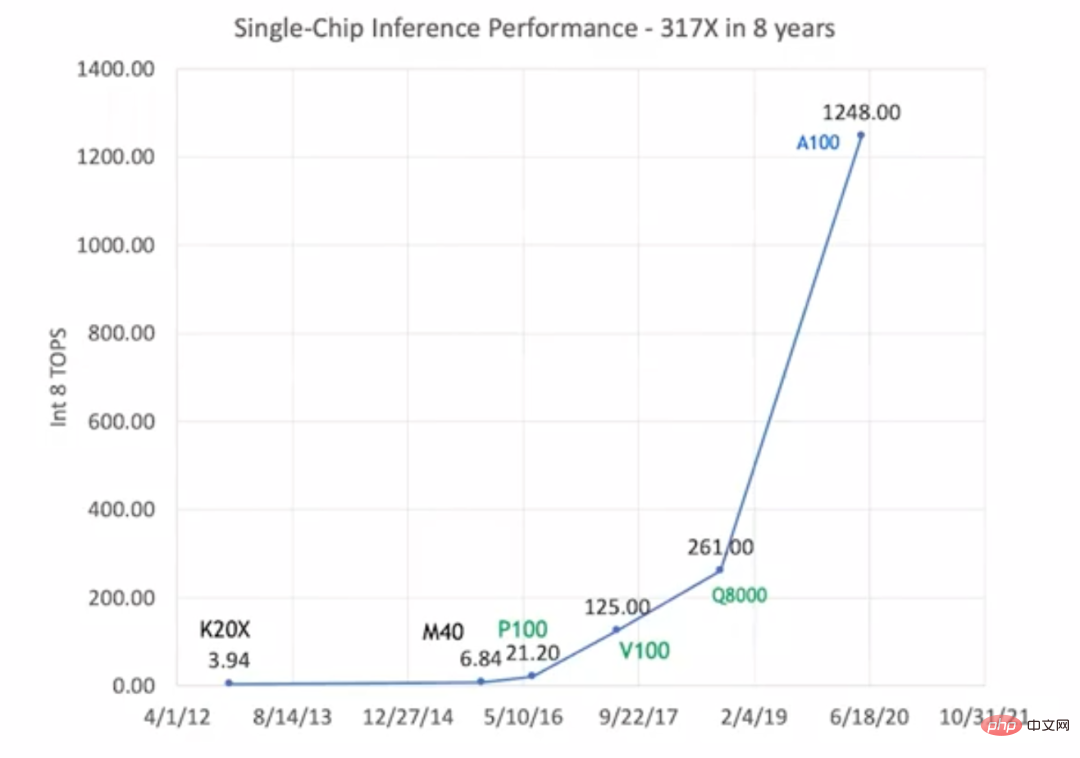

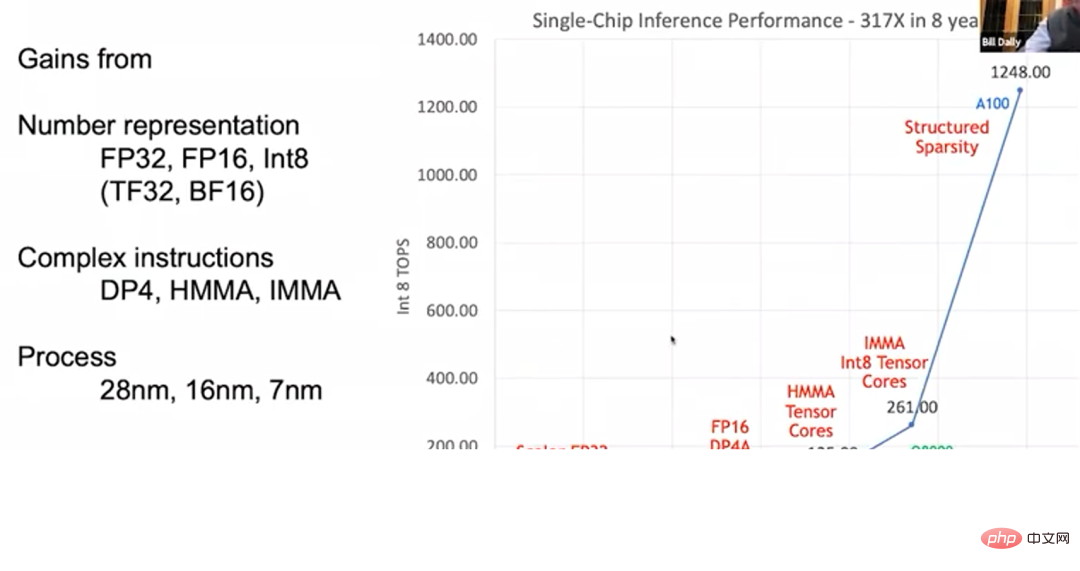

12012 年の K20X から 2020 年の A100 まで、GPU 推論性能が 317 倍に向上元の値。これは「ファンの法則」と呼ばれるもので、この発展速度は「ムーアの法則」よりもはるかに速いです。

GPU の推論性能が向上します ただし、「ムーアの法則」とは異なり、「ファンの法則」では、GPU の性能向上はプロセス技術の進歩に完全に依存しているわけではありません。上の図では、これらのタイプの GPU が黒、緑、青の色でマークされており、3 つの異なるプロセス テクノロジが使用されていることを表しています。初期の K20X と M40 は 28nm プロセスを使用し、P100、V100、Q8000 は 16nm プロセスを使用し、A100 は 7nm プロセスを使用しました。プロセス テクノロジの進歩によって GPU パフォーマンスを向上できるのは、元のレベルの 1.5 倍または 2 倍までです。全体的な 317 倍のパフォーマンス向上は、主に GPU アーキテクチャと回路設計の改善によるものです。

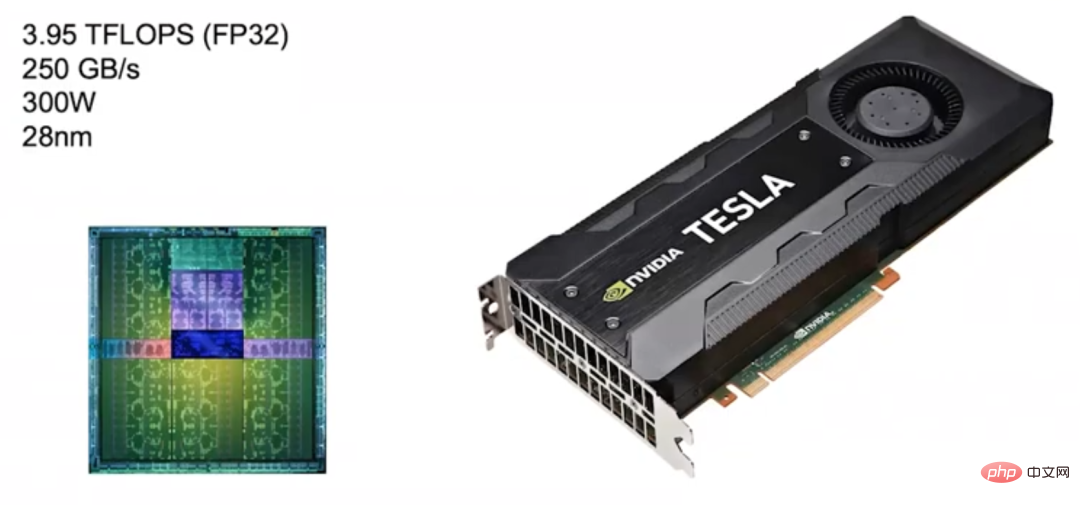

NVIDIA は 2012 年に Kepler アーキテクチャの GPU を発売しましたが、これはディープ ラーニング専用に設計されたものではありませんでした。 Nvidia がディープ ラーニングに取り組み始めたのは 2010 年で、当時はまだ GPU 製品をディープ ラーニング用にカスタマイズすることを検討していませんでした。

ケプラー (2012) ケプラー対象利用シーンは画像処理やハイパフォーマンスコンピューティングですが、主に画像処理に使用されます。そのため、浮動小数点演算能力が高く、FP32演算(単精度浮動小数点演算)速度は4TFLOPS近く、メモリ帯域幅は250GB/sに達するという特徴があります。 Kepler の優れたパフォーマンスに基づいて、NVIDIA もそれを自社製品のベースラインとみなしています。

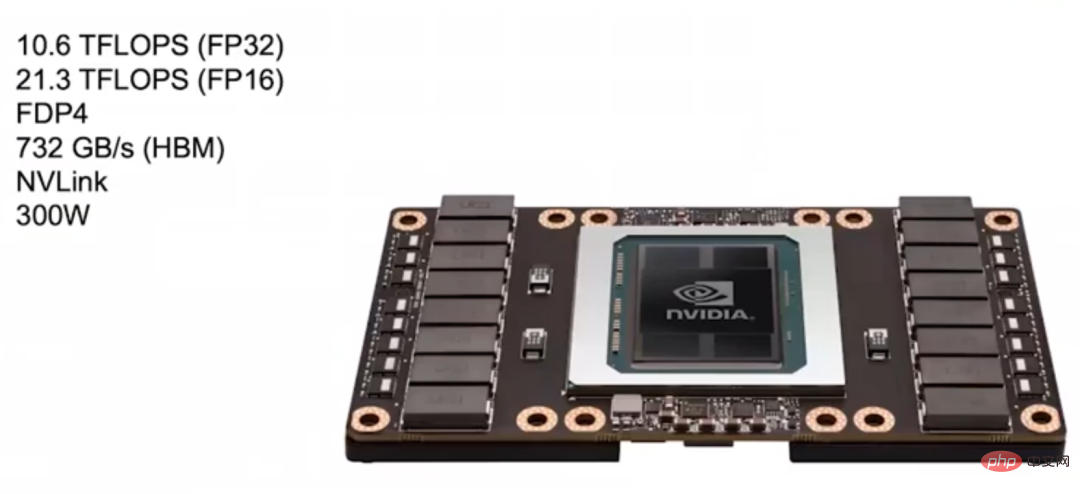

Pascal (2016) その後、Nvidia が 2016 年に発売しました。 Pascal アーキテクチャでは、その設計がディープラーニングにより適しています。 NVIDIA は調査の結果、多くのニューラル ネットワークが FP16 (半精度浮動小数点計算) でトレーニングできることを発見したため、Pascal アーキテクチャのほとんどのモデルが FP16 計算をサポートしています。

下の図にあるこの Pascal GPU の FP32 計算速度は 10.6 TFLOPS に達することができ、これは以前の Kepler GPU よりもはるかに高く、FP16 計算はさらに高速であり、 FP32は2回。

Pascal アーキテクチャは、FDP4 などのより複雑な命令もサポートしているため、命令のフェッチ、デコード、オペランドのフェッチのオーバーヘッドを 8 つの算術演算に分割できます。オーバーヘッドを 2 つの算術演算にのみ割り当てることができる以前の融合乗加算 (Fuse Multiply-Add) 命令と比較して、Pascal アーキテクチャは追加のオーバーヘッドによって生じるエネルギー消費を削減し、代わりにそれを数学演算に使用できます。

Pascal アーキテクチャでは、HBM ビデオ メモリも使用されており、帯域幅は 732 GB/秒で、これは Kepler の 3 倍です。帯域幅を増やす理由は、ディープ ラーニングのパフォーマンスを向上させる上でメモリ帯域幅が主なボトルネックになるためです。さらに、Pascal は NVLink を使用してより多くのマシンと GPU クラスターを接続し、大規模なトレーニングをより適切に完了します。

NVIDIA がディープラーニング向けに発売した DGX-1 システムは、Pascal アーキテクチャに基づいた 8 つの GPU を使用します。

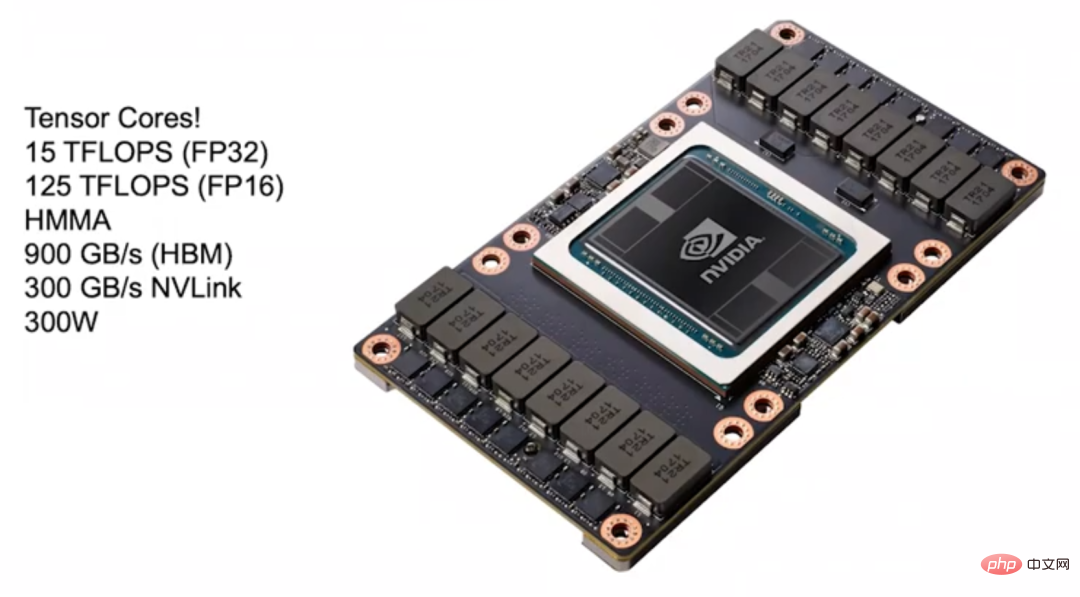

ボルタ (2017) 2017 2017 年に NVIDIA はディープ ラーニングに適した Volta アーキテクチャを発表しましたが、その設計の焦点の 1 つは命令のオーバーヘッドをより適切に償却することです。 Tensor Core は、深層学習を高速化するために Volta アーキテクチャに導入されています。 Tensor コアは命令の形式で GPU に接続できます。重要な命令は HMMA (Half Precision Matrix Multiply Accumulate) で、これは 2 つの 4×4 FP16 行列を乗算し、その結果を 1 つに加算します。FP32 行列では、この種の演算が行われます。深層学習では非常に一般的です。 HMMA 命令を使用すると、命令のフェッチとデコードのオーバーヘッドを償却によって元の 10% ~ 20% に削減できます。

残りは負荷の問題です。 Tensor Core のパフォーマンスを超えたい場合は、負荷に取り組む必要があります。 Volta アーキテクチャでは、ディープラーニングの高速化に大量のエネルギー消費とスペースが使用されるため、プログラマビリティを犠牲にしても、大きなパフォーマンス向上は得られません。

Volta は、メモリ帯域幅 900 GB/秒の HBM ビデオ メモリもアップグレードし、クラスタ構築時に帯域幅を 2 倍にできる新しいバージョンの NVLink も使用しました。さらに、Volta アーキテクチャには複数の GPU を接続できる NVSwitch も導入されており、理論上、NVSwitch は最大 1024 個の GPU を接続して大規模な共有メモリ マシンを構築できます。

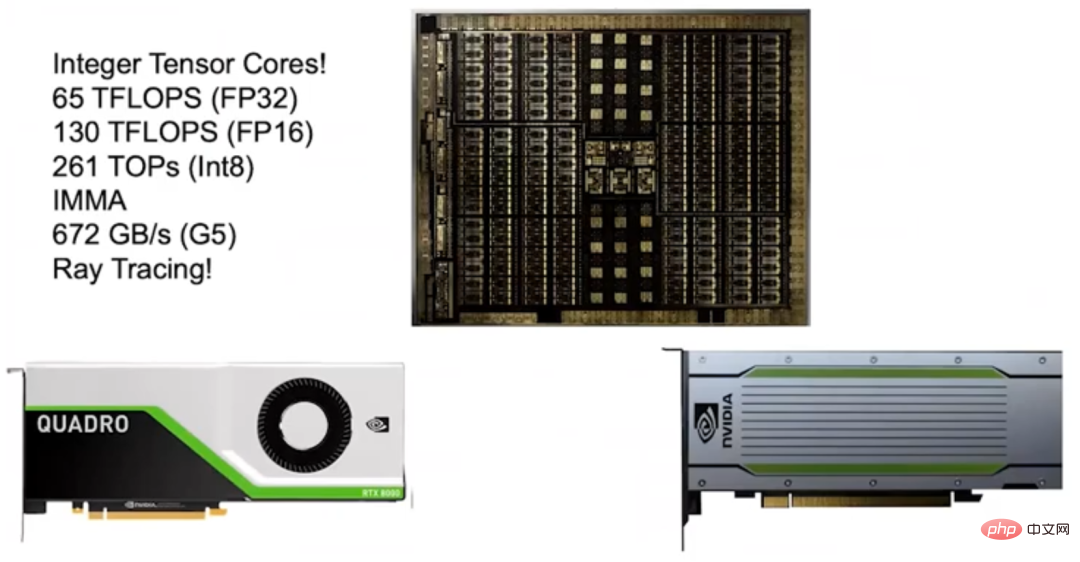

チューリング (2018) 2018 2016 年、NVIDIA は Turing アーキテクチャを発表しました。以前の Tensor コアの大成功を受けて、NVIDIA は Integer Tensor コアを発売しました。ほとんどのニューラル ネットワークは FP16 でトレーニングでき、推論にはそれほど高い精度と大きなダイナミック レンジは必要ないため、Int8 を使用するだけです。したがって、NVIDIA は、Turing アーキテクチャに Integer Tensor コアを導入し、パフォーマンスを 2 倍にしました。

Turing アーキテクチャでは、GDDR メモリも使用して、高帯域幅要件を持つ NLP モデルと推奨システムをサポートします。当時、Turing アーキテクチャのエネルギー効率が市場の他の加速器ほど良くないことに疑問を抱く人もいました。しかし、慎重に計算すると、他のアクセラレータが LPDDR メモリを使用するのに対し、Turing アーキテクチャは G5 ビデオ メモリを使用するため、実際にはよりエネルギー効率が高いことがわかります。私の考えでは、G5 メモリを選択することは正しい決断でした。なぜなら、同様の製品ではサポートできない高帯域幅要件のモデルをサポートできるからです。

私が Turing アーキテクチャを心から誇りに思っているのは、レイ トレーシングをサポートする RT コアも搭載されていることです。 Nvidia が RT Core の研究を開始したのは 2013 年で、わずか 5 年後に RT Core を正式に発表しました。

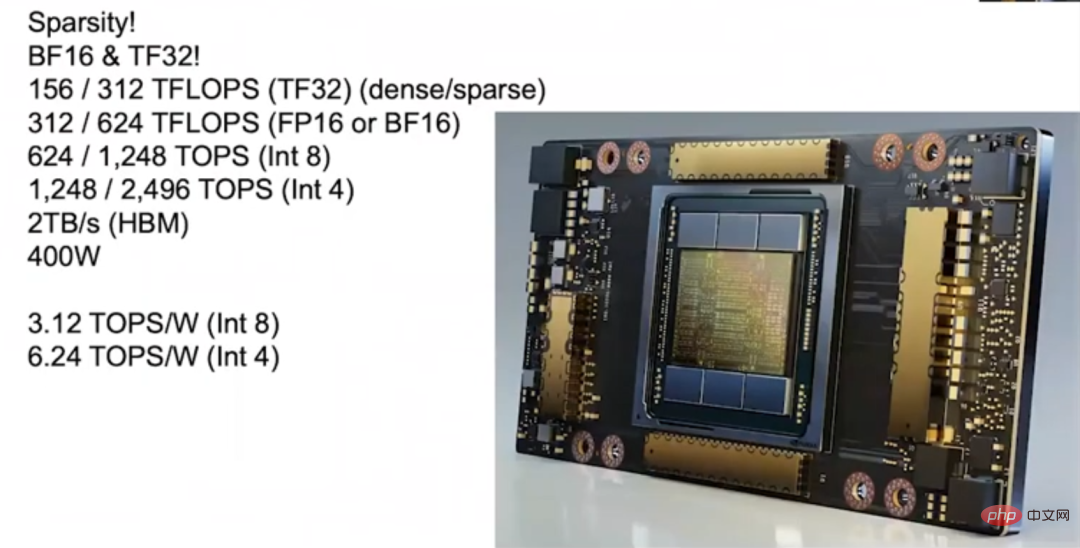

Ampere (2020) 2020 年、NVIDIA は Ampere をリリースしました。このアーキテクチャにより、その年にリリースされた A100 は、1,200 テラフロップスを超える推論速度という飛躍的なパフォーマンスを実現しました。 Ampere アーキテクチャの大きな利点の 1 つは、スパース性をサポートしていることです。ほとんどのニューラル ネットワークはスパース化できる、つまり、ニューラル ネットワークを「枝刈り」して、精度に影響を与えることなく多数の重みを 0 に設定できることがわかりました。ただし、異なるニューラル ネットワークは異なる程度でスパース化される可能性があるため、少し注意が必要です。たとえば、精度を損なうことなく、畳み込みニューラル ネットワークの密度を 30% ~ 40% に減らすことができますが、完全に接続されたニューラル ネットワークの密度は 10% ~ 20% に減らすことができます。

従来の考え方では、疎行列パッケージの操作にはオーバーヘッドが大きいため、密度を 10% 未満に下げることができない場合、トレードオフは密行列パッケージを操作する場合ほど良くないということです。パッケージ。私たちは最初にスタンフォード大学と協力してスパース性を研究し、その後マトリックス密度が 50% に達したときに効率的に実行できる非常に優れたマシンを構築しましたが、パワー ゲーティングの観点からスパース マトリックスを高密度マトリックスよりも効率的にすることは依然として困難です。マトリックスをより優れたものにするために、私たちは常にこの点を突破したいと考えています。

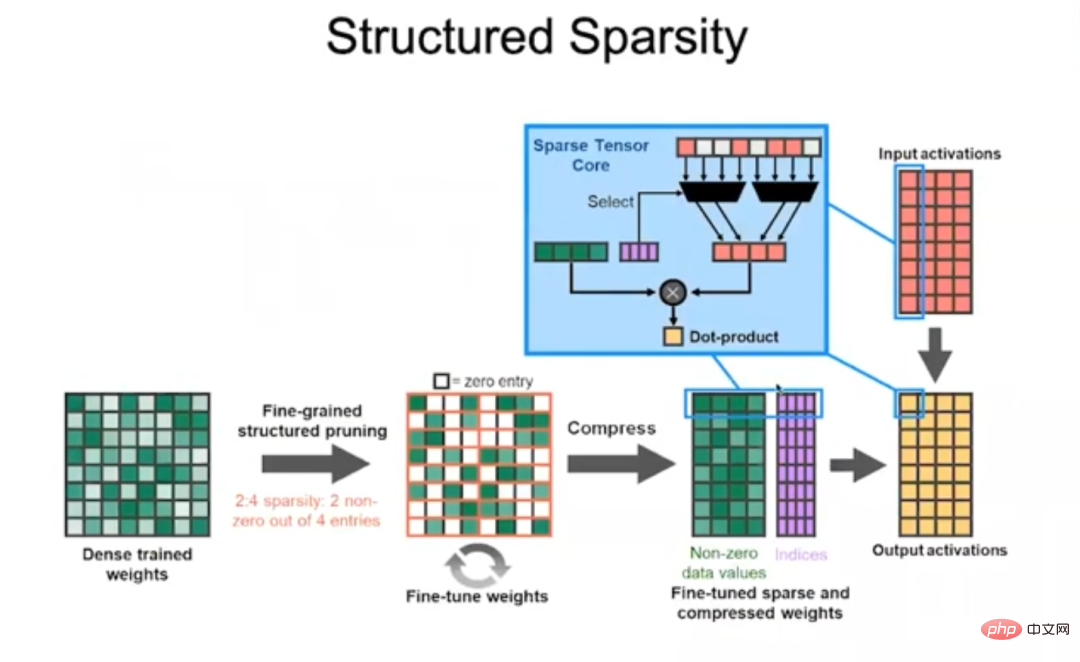

最終的に、私たちは問題を克服して Ampere を開発しました。その秘密は構造化されたスパーシティです。

構造化スパース Ampere アーキテクチャでは、次の 4 つの要素ごとに次のことを規定しています。行列 数値には、2 つを超える非ゼロ値を含めることはできません。つまり、重みは、非ゼロ値を削除することによって圧縮されます。コード ワード (コード ワード) を入力することでどの重みを保持するかを決定し、コード ワードを使用してこれらのゼロ以外の重みにどの入力アクティベーションを乗算するかを決定し、それらを加算してドット乗算演算を完了します。このアプローチは非常に効率的であり、Ampere アーキテクチャによりほとんどのニューラル ネットワークのパフォーマンスが 2 倍になります。

さらに、Ampere アーキテクチャには多くの革新があり、たとえば、Ampere には FP32 の 8 ビット指数ビットと、 FP16 の 10 ビットの指数ビット、仮数部の桁。 Ampere は BFLOAT 形式もサポートしており、BFLOAT の指数ビットは FP32 と同じですが、仮数ビットが FP32 より少ないため、FP32 の縮小版とみなすことができます。上記のデータ形式はすべて構造化スパースをサポートしているため、トレーニングに FP16 と TF32 を使用する場合でも、推論に Int8 と Int4 を使用する場合でも、構造化スパースによってもたらされる高いパフォーマンスを得ることができます。

Ampere の量子化能力はますます向上しており、多くのニューラル ネットワークに適用でき、高いパフォーマンスを保証できます。 Ampere には 6 つの HBM スタックがあり、HBM メモリの帯域幅もアップグレードされ、2TB/s に達しました。エンドツーエンドの推論中、Ampere のコンピューティング能力は 3.12 TOPS/W (Int8) および 6.24 TOPS/W (Int4) に達します。

GPU 推論パフォーマンス向上の 3 つの主要要素 これまでのディープラーニングの開発をまとめると、GPU 推論パフォーマンスは 8 年間で 317 倍に向上大きな要因:

#最初で最も重要なのは、数値表現の発達です。

#FP32 の精度が高すぎるため、算術演算のコストが高くなりすぎます。その後、Turing アーキテクチャと Ampere アーキテクチャが Int8 をサポートし、GPU のワットあたりのパフォーマンスが大幅に向上しました。 Google が TPU1 を発表する論文を発表したとき、TPU1 の利点は機械学習に特化して調整されていることであると述べました。実際、Google は自社の TPU1 と NVIDIA の Kepler を比較しているはずです (前述したように、Kepler はディープラーニング専用に設計されていません) で、FP32 と比較した場合、TPU1 の利点は Int8 の利点であると言えます。

第 2 に、GPU は複雑な命令をサポートしています。

#Pascal アーキテクチャにはドット乗算命令が追加され、Volta、Turing、Ampere アーキテクチャにはオーバーヘッドの共有を可能にする行列積命令が追加されました。プログラマブル エンジンを GPU に保持すると、多くの利点がもたらされ、各命令が非常に多くのタスクを完了するため、命令ごとのオーバーヘッドの償却がほとんど無視できるため、アクセラレータと同じくらい効率的になります。

#最後に、プロセス技術の進歩です。

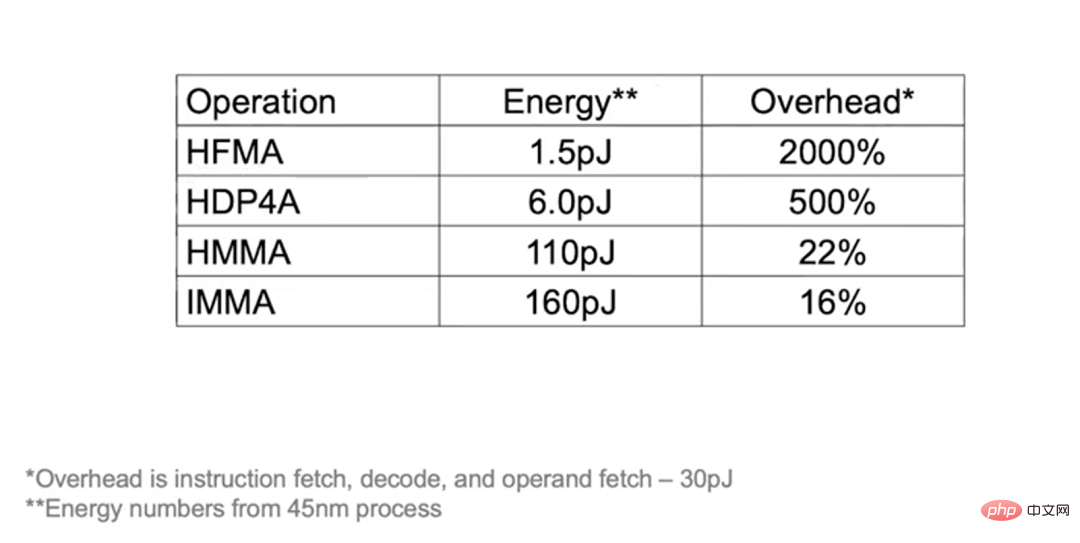

チップ製造プロセスの 28 ナノメートルから現在の 7 ナノメートルへの発展は、GPU のパフォーマンスの向上に一定の貢献をしました。次の例は、コスト共有の効果をよりよく理解するのに役立ちます。HFMA 演算を実行する場合、命令のフェッチ、デコード、オペランドの取得に必要な「乗算」および「加算」演算の合計はわずか 1.5pJ (ピコジュール、ピコジュール) です。 30pJ のオーバーヘッドが発生し、償却後のコストは 2000% にもなります。

HDP4A オペレーションを実行する場合、オーバーヘッドを 8 つのオペレーションに割り当て、オーバーヘッドを 500% に削減できます。 HMMA 操作の場合、エネルギー消費のほとんどが負荷に使用されるため、オーバーヘッドはわずか 22% ですが、IMMA はさらに低く、16% です。したがって、プログラマビリティを追求すると多少のオーバーヘッドが追加されますが、別の設計を採用することで達成できるパフォーマンスの向上の方が重要です。

上記は単一の GPU のパフォーマンスについて説明していますが、大規模な言語モデルをトレーニングするには明らかに複数の GPU が必要なので、GPU 間の接続も改善する必要があります。 Pascal アーキテクチャに NVLink を導入し、その後 Volta アーキテクチャでは NVLink 2 を採用し、Ampere アーキテクチャでは NVLink 3 を採用しました。各世代のアーキテクチャの帯域幅は 2 倍になりました。さらに、NVSwitch の第 1 世代を Volta アーキテクチャで、第 2 世代を Ampere アーキテクチャでリリースしました。 NVLink と NVSwitch を通じて、非常に大規模な GPU クラスターを構築できます。さらに、DGXボックスも発売しました。

DGX ボックス

2020 年に、Nvidia は Mellanox を買収したため、大規模な GPU クラスターを構築するためのスイッチやインターコネクトを含む、データセンター ソリューションの完全なセットを提供できるようになりました。さらに、AI Performance Record 500 リストでトップ 20 にランクされる DGX SuperPOD を搭載しています。以前は、ユーザーはマシンをカスタマイズする必要がありましたが、現在では、DGX SuperPOD を展開できる事前構成されたマシンを購入するだけで、DGX SuperPOD によってもたらされる高いパフォーマンスを得ることができます。さらに、これらのマシンは科学技術計算にも適しています。

これまでは、1 台のマシンで 1 つの大規模な言語モデルをトレーニングするには数か月かかっていましたが、GPU クラスターを構築することでトレーニング効率が大幅に向上するため、GPU クラスターの接続を最適化し、単一 GPU のパフォーマンスを向上させることも同様に重要です。

NVIDIA のアクセラレータの研究開発作業について話しましょう。 Nvidia はアクセラレータを新しいテクノロジをテストするためのキャリアと見なしており、成功したテクノロジは最終的にメインストリーム GPU に適用されます。アクセラレータは次のように理解できます: メモリ階層によって入力される行列乗算ユニットがあり、次に行うべきことは、エネルギー消費のほとんどをデータ処理ではなく行列乗算の計算に使用することです。

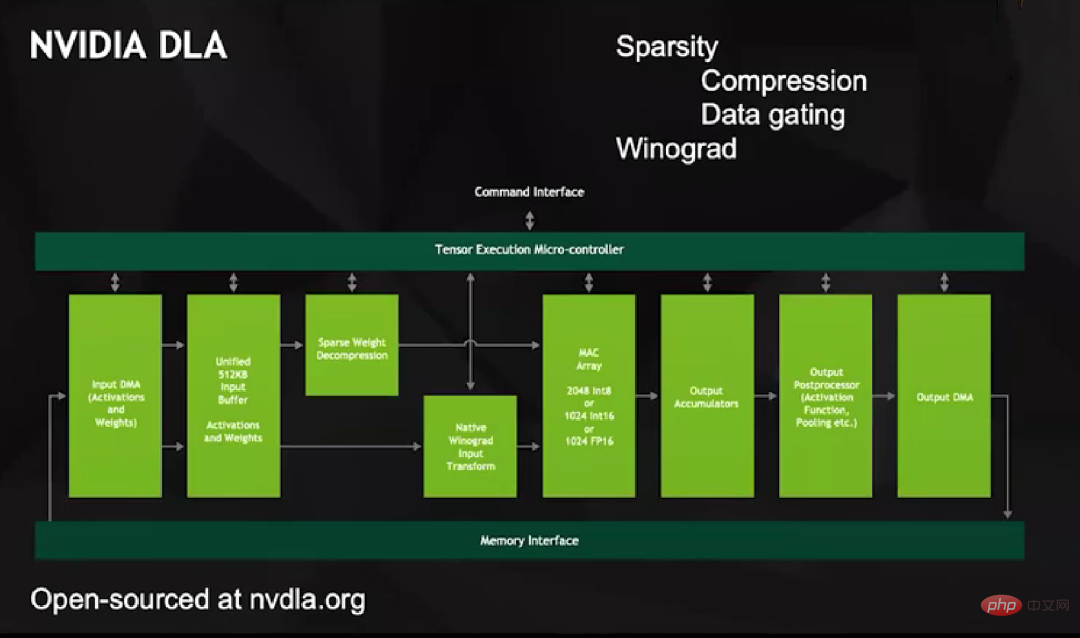

この目標を達成するために、私たちは 2013 年頃に NVIDIA DLA プロジェクトを立ち上げました。これは非常に完全なサポート機能を備えたオープン ソース製品であり、他の深層学習アクセラレータと何ら変わりはありません。ただし、DLA には、2048 個の Int8、1024 個の Int16、または 1024 個の FP16 操作をサポートする大規模な MAC アレイがあります。

DLA には 2 つの独自の機能があります。まず、スパース化をサポートします。簡単な成果から始めます。DMA から統合バッファー、および統合バッファーから MAC 配列を含むすべてのデータ転送には、ゼロ以外の値のみが含まれます。エンコードによってどの要素が残るかを決定し、これらの要素を解決します。圧縮そして計算のために MAC 配列に入力します。

DLA の解凍方法は賢明で、一連のデータがゼロになるため、MAC 配列にゼロ値を入力しません。代わりに、ゼロ値を表す別のラインを設定し、乗算器がいずれかの入力でそのラインを受信すると、乗算器内のデータをラッチして、数値が増加しない出力を送信します。ゲート制御は非常にエネルギー効率が高くなります。

2 つ目は、ハードウェア レベルで Winograd 変換をサポートすることです。ご存知のとおり、畳み込みを実行する場合、たとえば m×n 畳み込みカーネルの場合、空間領域では n 2 個の乗算器と加算器が必要ですが、周波数領域で実行する場合は、ポイントごとに必要なだけです。乗算。したがって、大規模なコンボリューション カーネル操作は、空間領域よりも周波数領域の方が効率的です。コンボリューション カーネルのサイズに応じて、Winograd 変換により一部の画像ネットワークのパフォーマンスが 4 倍向上します。

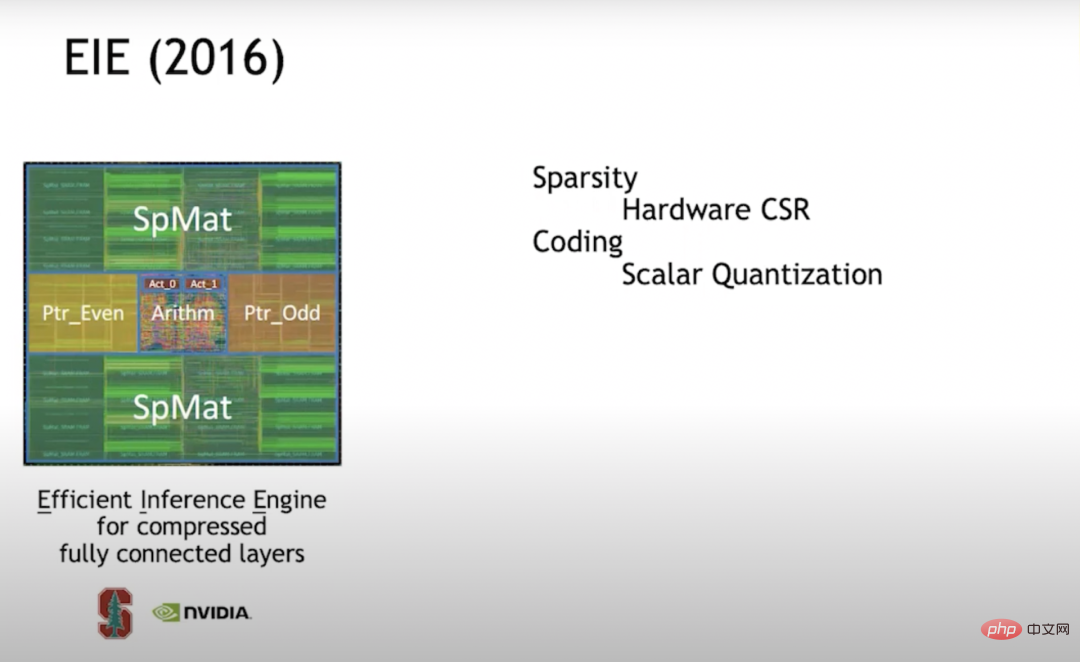

EIE (2016) 2016 年、私はスタンフォード大学で学びましたそして私の当時の学生である Han Song (MIT EECS の助教授で Shenjian Technology の元共同創設者) は一緒に EIE (Efficient Inference Engine) を研究しました。これは、スパース化に関する最初の調査の 1 つでした。ハードウェア レベルで CSR (Compressed Sparse Row) 行列表現をサポートしています。このアプローチは非常に効率的です。密度が 50% の場合、フル密度コンピューティングよりもさらに省エネになります。

アクセラレータの効率を高めたい場合は、各エンジンが単一の積和演算を実行するだけでなく、それぞれの積和演算を実行できるようにベクトル ユニット配列を構築する必要があることが後でわかりました。 PE (Processing Element) は 16×16=256 回の乗算と加算を実行します。しかし、ベクター セル アレイの構築を開始したとき、スパース性を効率的に実現するのは難しいことがわかり、構造化スパース性を採用することにしました。

EIE がスカラー ユニットを処理するとき、ポインター構造体を別のメモリに保存し、パイプライン ステージを通じてポインター構造体を処理し、どのデータを乗算できるかを決定してから、次の処理を実行します。乗算。演算の結果は適切な場所に配置されます。このプロセス全体は非常に効率的に実行されます。また、スパース性を実現するための「枝刈り」に加えて、ニューラル ネットワークの計算効率を向上させる方法には定量化も含まれることもわかりました。したがって、コードブック量子化を使用することにしました。コードブックの量子化は、ビットで表現されるデータの効率を向上させる最良の方法です。そこで私たちはコードブックを使ってトレーニングしました。

バックプロパゲーションを使用して勾配降下法を捕捉できれば、バックプロパゲーションをあらゆるものに適用できることがわかりました。そこで、コードブックでバックプロパゲーションを使用して、特定の精度に最適なコードワードのセットをトレーニングしました。コードブックが 7 ビットであると仮定すると、128 個のコードワードが得られるため、トレーニングに最適な 128 個のコードワードをニューラル ネットワークで見つけます。

コードブックの量子化は、数学的演算のオーバーヘッドが非常に大きいという問題に直面しています。コードブックがどれほど大きくても、実際の値が何であっても、RAM (ランダム アクセス メモリ) でそれを検索する必要があるからです。実際の値は高精度で表現される必要がありますが、これらのコードワードを正確に表現することはできません。そのため、私たちは高精度な数学に多くの努力を注ぎました。圧縮の観点から見ると、これは非常にうまく機能しますが、数学的エネルギーの観点から見ると、費用対効果があまり高くないため、その後の作業ではこのテクノロジーを放棄しました。

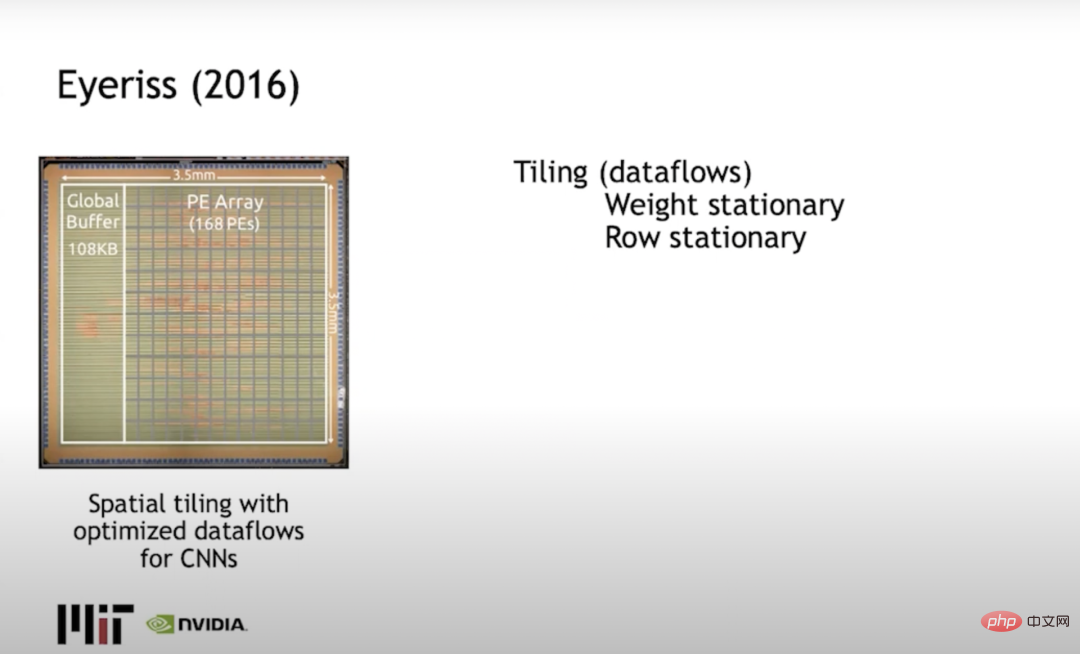

アイリス (2016) ジョエルMIT の Emer (Nvidia と MIT の両方で働いている) と Vivienne Sze は Eyeriss を構築しましたが、これは主にタイルの問題、つまりデータの移動を最小限に抑えるために計算を制限する方法を解決するものでした。一般的なアプローチは、固定行を使用し、行に重みを分散し、列に出力アクティベーションを分散し、データの移動によって消費されるエネルギーを最小限に抑えることです。

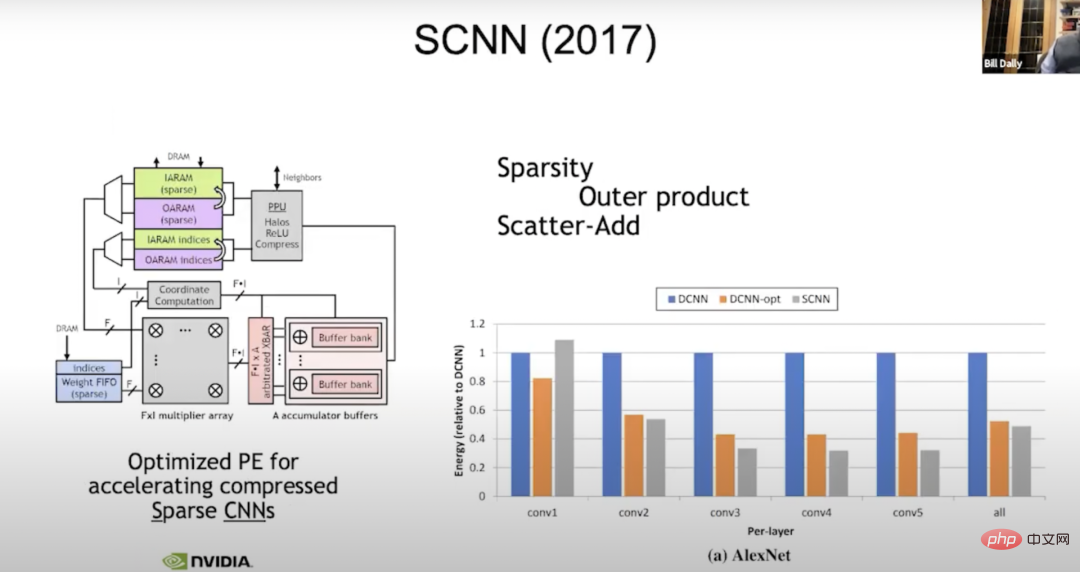

SCNN (2017) 私たちは現在もスパーシティに取り組んでいます。研究。 2017 年に、私たちはスパース コンパイル (ニューラル ネットワークの進化版) 用の SCNN (Sparse CNN) と呼ばれるマシンを構築しました。私たちがやったことは、スパース性の処理に関連するすべての複雑な問題を出力に移したということです。すべての入力アクティベーションを読み取り、どこに移動する必要があるかを判断します。つまり、ここでの「f 幅ベクトル」は典型的なベクトル入力アクティベーションです。

一度に 4 つの入力アクティベーション、4 つの重みを読み取ります。各重みは各入力アクティベーションで乗算する必要があります。結果をどこに置くかだけが問題なので、f に f を掛けます。

座標計算では、入力アクティベーションの指数と重みをとり、出力アクティベーションにおいて加算結果が必要な位置を計算します。次に、これらのアキュムレータ バッファに対してデータ スキャッタ (scatter_add) 計算が実行されます。それまでは、すべてが完璧に機能していました。しかし、実際には出力の精度が最も広いため、不規則性を出力に転送するのは得策ではないことがわかりました。蓄積する傾向がある場合は、8 ビットの重み付け、8 ビットのアクティブ化を実行し、合計は 24 ビットになります。ここでは、ワイド アキュムレータを使用して大量のデータ移動を実行します。これは、より集中的なデータ移動を実行するよりも優れています。ただし、その改善は想像ほどではなく、密度ユニットのエネルギーの 50% 程度でしょうか。

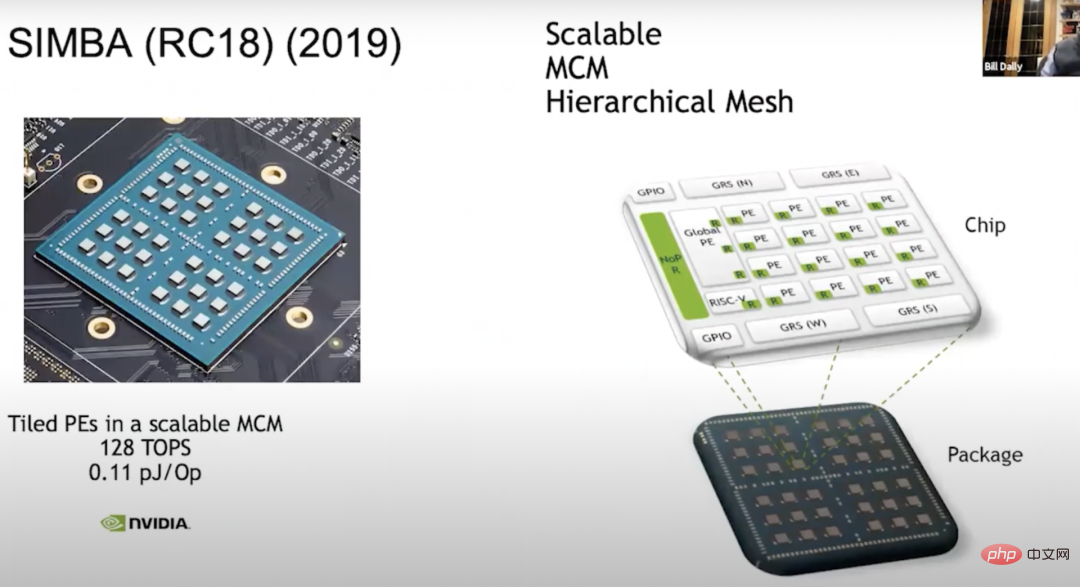

##シンバ(RC18)(2019) 私たちがしなければならないもう 1 つのことは、既存のアクセラレータを使用してマルチチップ モジュール - SIMBA (RC18) を構築することです。この研究を行うというアイデアは 2018 年に思いつきました。同時に、このチップも数々の独創的な技術を実証しました。これは優れた PE アーキテクチャを備えており、チップは中央で非常に効果的なシグナリング テクノロジを提供します。現在、アーキテクチャは完全な 36 チップに拡張されており、各チップには 4x4 PE マトリックスがあり、このユニット内では各 PE に 8 幅のベクトル ユニットがあるため、128 TOPS の計算能力を得ることができ、各 Op は 0.1 pJ です。は約 10 TOPS/W に相当します。

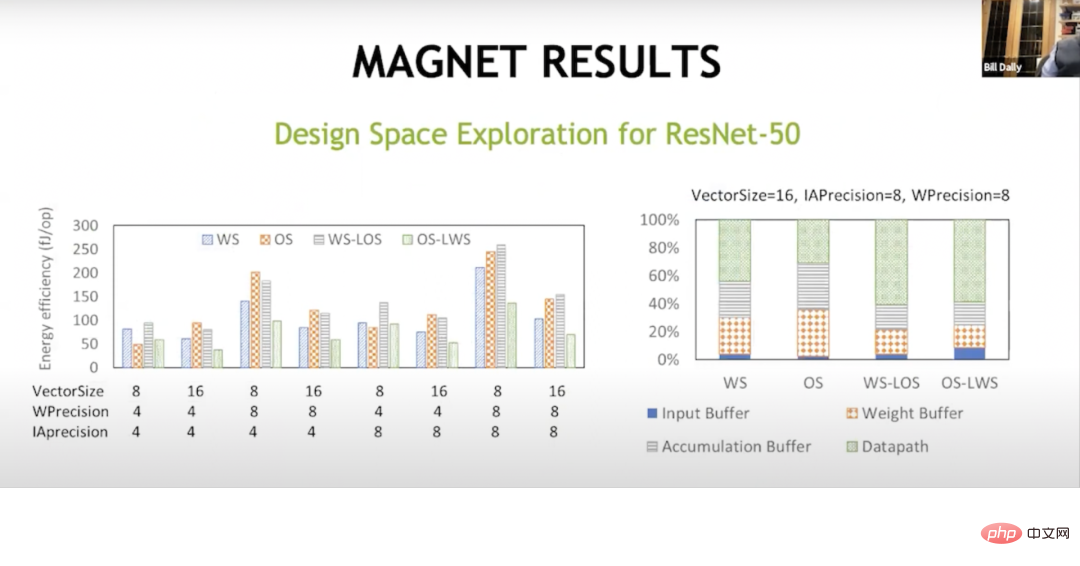

私たちはトレードオフについて多くのことを学びました。これらの PE アレイの構築は、メモリ階層の構築方法やデータのスケジュール方法など、非常に大規模な設計空間を構築することに似ていることに気づき、MAGNET と呼ばれるシステムを構築しました。

MAGNET 上の写真は、2019 年の ICCAD (コンピュータ支援設計国際会議) で公開された設計空間探索システムです。主に、各ベクトル ユニットの幅、各 PE のベクトル ユニットの数、重みバッファの大きさ、アキュムレータ バッファの大きさ、アクティベーション バッファの大きさなど、設計空間を列挙するために使用されます。その後、別のレベルのキャッシュを実行する必要があることがわかり、ウェイト コレクターとアキュムレーター コレクターを追加しました。

MAGNET の結果 この追加レベルのキャッシュにより、最終的には成功でした。これは、ここでのデータ フローが異なっており、重み固定データ フローはもともと Sze と Joel によって行われたものであることを示しています。エネルギーのほとんどを、蓄積バッファ、重みバッファ、入力バッファなど、データ パスの外側のものに費やしています。しかし、これらのハイブリッド データ フローを使用すると、重みが固定され、ローカル出力が固定され、出力が固定され、ローカルの重みが固定され、エネルギーのほぼ 3 分の 2 を数学演算で得ることができ、これらのメモリに費やされるエネルギーを削減できます。配列をメモリ内で階層の別のレベルで処理します。これにより、ワットあたりのパフォーマンスが約 20 TOPS になります。

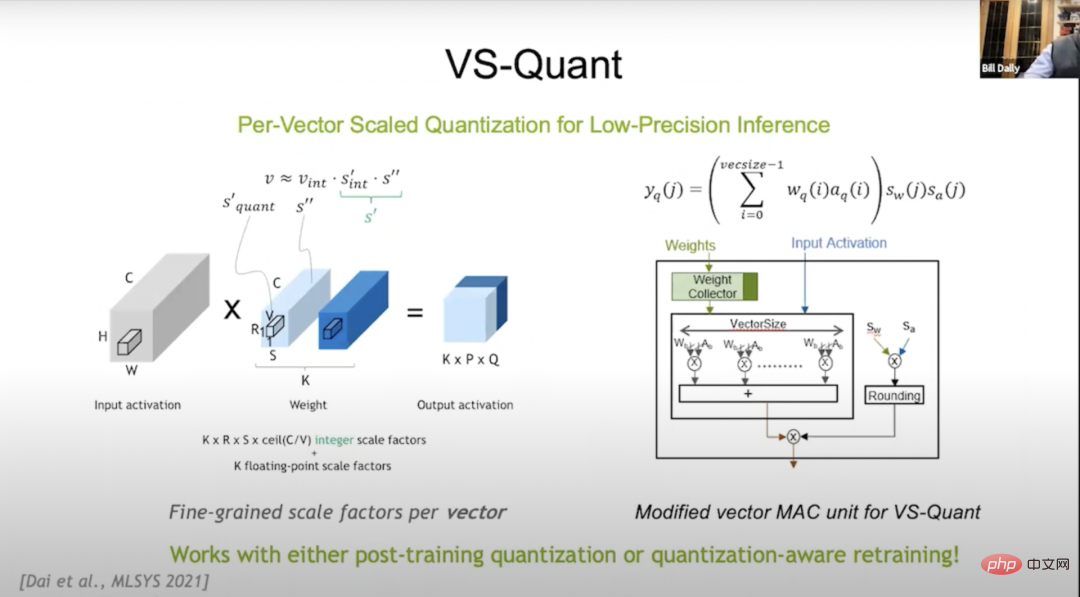

VS-Quant 2021 、 MLSYS (機械学習とシステムに関する会議、機械学習とシステム会議) で、ビット数を圧縮する方法 (この点でコードブックの量子化効果は非常に優れています) と定量的手法を検討するために VS-Quant を紹介しました。これは数学的オーバーヘッドの点で非常に費用対効果が高くなります。整数表現を使用しますが、整数のダイナミック レンジを表現できるようにそれをスケーリングしたいと考えています。

しかし、これをニューラル ネットワーク全体に適用すると、あまりうまく機能しないことがわかりました。ニューラル ネットワークにはさまざまなダイナミック レンジがあるためです。 VS-Quant の重要なポイントは、比較的小さなベクトルに 1 つのスケール係数を課すことです。ほぼ 32 の重みに対して上記の操作を実行することにより、ダイナミック レンジが大幅に小さくなります。これらの整数を先頭に置くことも、調整して最適化することもできます。

外れ値を正確に表現できなかった可能性がありますが、残りの数値はより正確に表現できました。このようにして、比較的低精度の重みとアクティベーションを交換して、より高い精度を得ることができます。したがって、複数のスケール係数ができました。1 つは重み係数、もう 1 つはアクティベーション係数です。

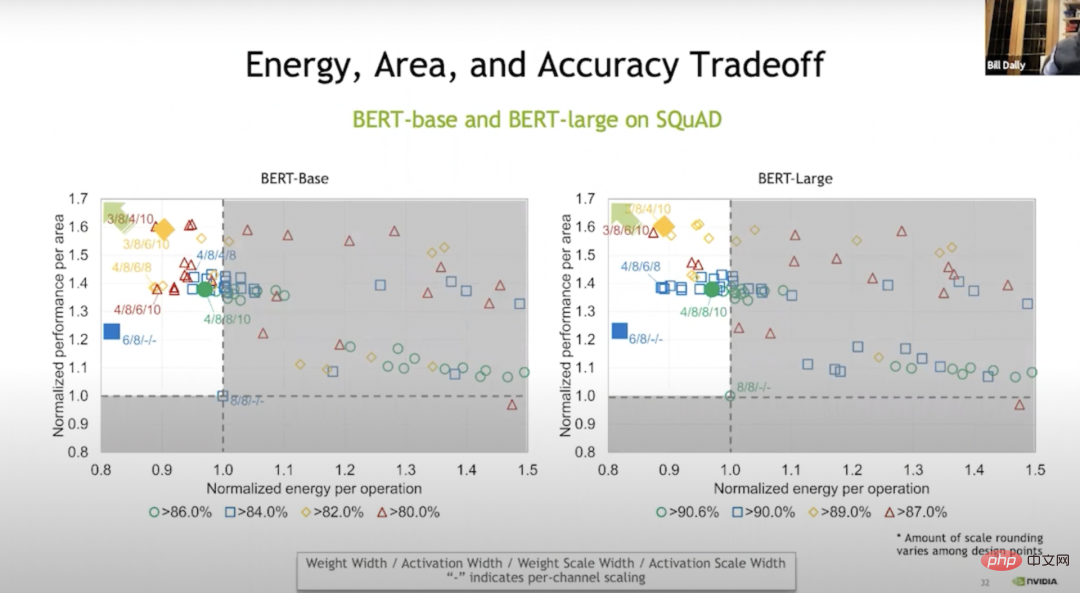

#エネルギー、面積、精度のトレードオフ # 基本的にこれらの操作はベクトル レベルで実行され、結果は Bert ベースで表示されます。ウェイトなしのトレーニングと比較して、トレーニングによって 20% のエネルギーと場合によっては 70% のスペースを節約できます。上図の緑色は基本的に精度の低下がないことを示し、青、オレンジ、赤は精度が向上していることを示します. 高いか低いか。しかし、青レベルでも精度はかなり高いです。

VS-Quant とその他の調整を加えて、これらの言語モデルで試行を実行しました。言語モデルでの実行は、約 120 TOPS/W の画像モデルでの実行よりもはるかに困難です。

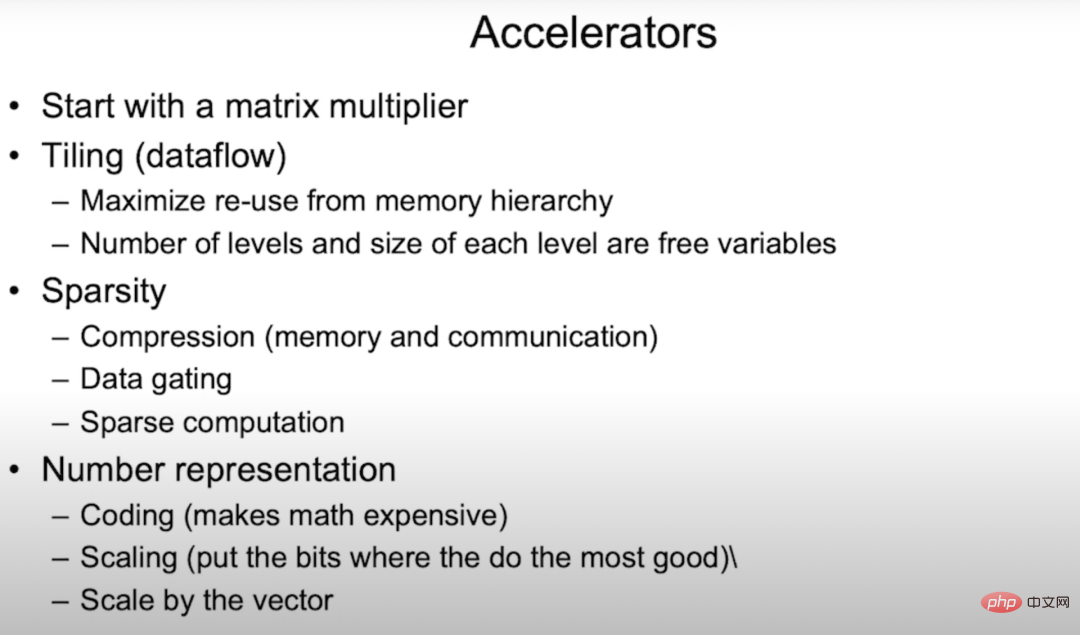

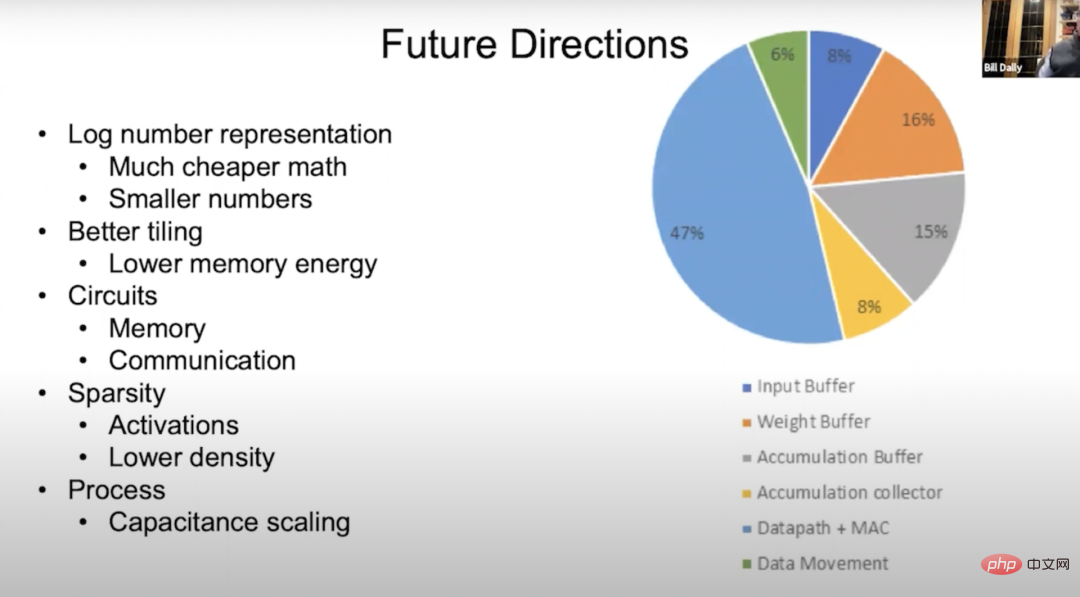

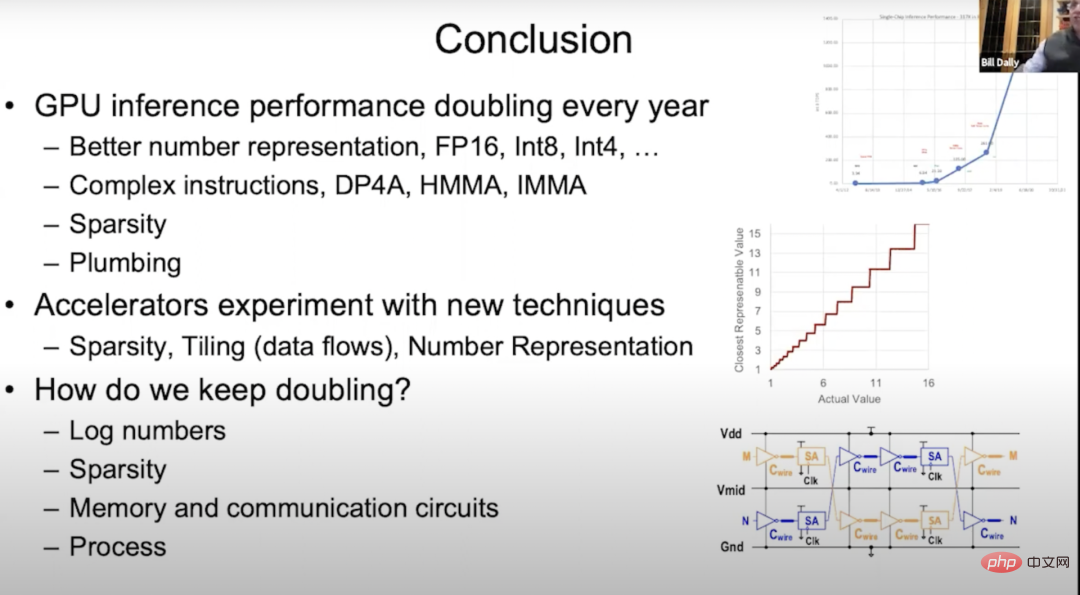

アクセラレータ したがって、アクセラレータについては、次のことを行う必要があります。行列乗算の最初のデバイス。タイリング法、つまりニューラル ネットワークを使用した 7 つのネストされたループ計算法を考え出す必要があります。基本的に、これらのループの一部をメモリ システムの各層にコピーして、各層のメモリ階層の再利用を最大化し、データ処理を最小限に抑えます。 圧縮に優れたスパース性についても研究しました。基本的に、メモリ帯域幅と通信帯域幅が増加し、メモリと通信のエネルギーが削減されます。スパース性開発の次のレベルは、値がゼロの場合、ループごとに 8 ビットまたは 16 ビットに切り替える必要がなく、ゼロ値を表す別の行を送信するだけです。 Ampere アーキテクチャは、構造化スパース性を使用して乗算器を再利用できます。これは、少数のマルチプレクサのオーバーヘッドのみを必要とする非常に効率的な方法です (これを除くと基本的に無視できます)。ポインター操作を行うときに乗算器を再利用することもでき、これによりパフォーマンスが 2 倍向上します。数値表現は非常に重要です。 EIE (訳者注: Efficient Inference Engine、ISCA 2016 での Han Song 博士の論文。圧縮されたスパース ニューラル ネットワークのハードウェア アクセラレーションを実装。近似手法を備えた ESE が FPGA2017 の最優秀論文を受賞) から始めて、コードブックを作成しようとしましたが、これにより、スケーリングが数学的に高価になります。 最後に、アクセラレータでのテストに成功したテクノロジーは、最終的には GPU に適用されることになります。これはテストに適した方法です。私たちは GPU がドメイン固有のハードウェア用のプラットフォームであると考えています。そのメモリ システムは非常に優れており、ネットワークはスムーズなので、ディープ ラーニング アプリケーションを非常に高速に実行できます。 ##将来の方向性 深層学習ハードウェアの将来について話しましょう。上の図はエネルギー フローの円グラフです。エネルギー フローの大部分がデータ パスに流れていることがわかります。その約 50% は数学的演算に関するものなので、数学的演算によるエネルギー消費を少なくしたいと考えています。残りはデータ パスに流れます。メモリとデータの移動。緑色のものはデータ転送で、残りは入力バッファ、重みバッファ、蓄積バッファ、および蓄積コレクタであり、比率は異なります。私たちは数学演算のエネルギー消費を削減することを検討しています。最良の方法の 1 つは、数学演算を対数システムに移行することです。対数系では乗算が加算になり、加算は通常、エネルギー消費量が大幅に少なくなるからです。もう 1 つの方法は、より小さい値に変換することです。これは、VS-Quant を通じて実現できます。より正確に量子化することで、精度の低い数値を使用したニューラル ネットワークから同等の精度を得ることができます。 私たちは、場合によってはメモリ階層にさらに多くの層を追加するなど、メモリのエネルギーを削減し、メモリ回路を作成できるように、タイリングをさらに改善したいと考えています。通信回路がより効率的になります。 Ampere アーキテクチャに関しては、構造化スパース性に関してすでに行っている作業は良いスタートですが、密度を下げるか、複数の密度を選択してアクティベーションと重みを調整することで、より良い結果が得られると思います。研究の深化に伴い、プロセス技術も静電容量のスケーリングにある程度の進歩をもたらすでしょう。 2012年リリースKepler アーキテクチャ以来、GPU 推論のパフォーマンスは毎年 2 倍になっています。この発展は主に、ますます優れたデジタル表現によるものです。今回は、Kepler アーキテクチャの FP32 から FP16、Int8、そして Int4 まで、命令オーバーヘッドを割り当てることでより複雑なドット積を使用することについて、Pascal アーキテクチャと準Volta アーキテクチャでは高精度行列の乗算と累算、Turing アーキテクチャでは整数行列の乗算と累算、Ampere アーキテクチャでは構造的スパース性が挙げられます。 これまで配管についてはほとんど話してきませんでしたが、配管は非常に重要です。強力な Tensor コアを最大限に活用できるように、オンチップ メモリ システムとネットワークをレイアウトするために配管が使用されます。 Tensor コアがチューリング アーキテクチャで 1 秒あたりギガビットの演算を実行し、一般的なベンチマークの実行にデータを供給するには、ブランチ メモリ、オンチップ メモリ、およびそれらと通常動作の間の相互接続を配置することが非常に重要です。 将来に向けて、さまざまな新技術を加速器に応用していきたいと考えています。前述したように、MAGNet プロジェクトでは、スパース性とタイリング技術について多くの実験を行い、さまざまなタイリング技術、数値表現などを試してきました。しかし、ディープラーニングの進歩は実際にはハードウェア性能の継続的な向上に依存しているため、私たちは依然として大きなプレッシャーを感じており、GPU の推論性能を毎年 2 倍にすることは大きな課題です。 実際、私たちの手札はほとんど使われていないため、新しい技術の開発に着手する必要があります。注目に値すると私が考える 4 つの方向性は次のとおりです。 #まず、対数 (対数) などの新しい数値表現と、EasyQuant よりも賢い量子化スキームを学習します。 ##2 番目に、スパース性についてさらに詳しく学習します。 #次に、ストレージ回路と通信回路を学習します。 7 視聴者の質問に答える デヤン ミロジッチ: 変換するにはどのくらいの大きさの行列畳み込みが必要かWinograd アルゴリズム より効率的な畳み込み実装に変換しますか? 3x3 行列の畳み込みは非常に効率的だと思います。もちろん、畳み込みが大きいほど効率は高くなります。 Bill Dally: 各 HBM スタックには、Ampere などの個別のフレームバッファ領域があります。アーキテクチャには 6 つのスタックがあります。メモリ帯域幅は、各メモリ コントローラが全帯域幅で動作している状態で計算されます。各 GPU コア間にはキャッシュ層があり、オンチップ ネットワークの帯域幅は HBM 帯域幅の数倍であるため、基本的に HBM を飽和させるにはストリーミング マルチプロセッサのごく一部を実行するだけで済みます。 Bill Dally: データとスレッドをどこに配置するかはプログラマーが決定します場所を指定すれば、GPU 上でスレッドとデータを開始し、それらが実行される場所を決定するだけです。 NVLink を使用して接続されたシステムの主な利点は、NVLink が共有アドレス空間であり、比較的小さなデータを送信するオーバーヘッドも非常に小さいことです。そのため、ネットワーク内でクラスター通信を使用します。 通常、ディープ ラーニングでデータ並列処理を行う場合、各 GPU は同じネットワークを実行しますが、同じデータ セットの異なる部分を処理し、それぞれ重み勾配を蓄積します。 GPU 全体で勾配を共有し、すべての勾配を蓄積してから重みに追加します。クラスター通信は、この種の作業の処理に非常に優れています。 Dejan Milojicic: すべてのアプリケーション向けに汎用のディープ ラーニング アクセラレータを作成すべきか、それともビジョン アクセラレータや自然言語処理アクセラレータなどの個別の専用アクセラレータを作成すべきか? ? ビル・ダリー: 効率に影響を与えなければ、アクセルはもちろんだと思います。汎用性が高いほど優れており、Nvidia の GPU は、ディープ ラーニングの効率を加速する点で専用アクセラレータに匹敵します。本当に重要なことは、機械学習の分野が信じられないほどのペースで進歩しているということです。 数年前、誰もがまだリカレント ニューラル ネットワークを使用して言語を処理していました。その後、Transformer が登場し、電光石火の速さで RNN に取って代わりました。瞬く間に、誰もが Transformer を使用し始めました。処理、自然言語処理。同様に、ほんの数年前までは、誰もが CNN を使用して画像を処理していましたが、多くの人が今でも畳み込みニューラル ネットワークを使用していますが、画像処理に Transformer を使用する人が増えています。 したがって、製品を過度に特化したり、特定のネットワーク専用のアクセラレータを作成したりすることは支持しません。製品の設計サイクルには通常数年かかり、その間、人々はその製品の使用をやめてしまう可能性が高いからです。ネットワーク。業界は常に驚くべき速度で発展しているため、業界の変化をタイムリーに検出する鋭い目を持たなければなりません。 Dejan Milojicic: ムーアの法則は GPU のパフォーマンスとメモリ使用量にどのような影響を与えますか? ビル・ダリー: ムーアの法則によると、トランジスタのコストは年々減少します。年によります。今日、集積回路上に収容できるトランジスタの数は確実に増加しており、チップの製造プロセスも 16 ナノメートルから 7 ナノメートルへと飛躍的に進歩しており、集積回路上のトランジスタの密度はますます大きくなっていますが、価格は大幅に上昇しています。単一トランジスタの数は減少していません。したがって、ムーアの法則は少し時代遅れだと思います。 それでも、より大きな GPU を構築できるように、集積回路上により多くのトランジスタを搭載することは良いことです。大型の GPU はより多くの電力を消費し、より高価になりますが、以前は構築できなかったものを構築できるようになるため、これは常に良いことです。 Dejan Milojicic: 開発者が PyTorch のようなフレームワークにもっと注目する場合、深層学習モデルをより適切に実行するためにハードウェアの進歩から何を学べばよいでしょうか?効率的? ビル・ダリー: この質問は答えるのが難しいです。フレームワークはハードウェアをうまく抽象化しますが、モデルの実行速度に影響を与える要因がいくつかあり、調査する価値があります。私たちができることは、より良い数値表現など、より良い手法を思いついたときに、フレームワークにさまざまな異なる手法を組み合わせて、どれがより効果的であるかを確認することです。これは研究開発作業に不可欠な部分です。 Dejan Milojicic: Nvidia は新しいパッケージング方法を実験していますか? Bill Dally: 私たちは、さまざまなパッケージング技術についてさまざまな実験を行ってきました。実験して何ができ、何ができないかを把握して、適切な時期に本番環境にデプロイできるようにします。例えば、これらのプロジェクトの中には、はんだバンプやチップの積層にハイブリッドボンディングを使用するマルチチップモジュールを研究しているものもあり、実際には、単純なパッケージング技術も数多く存在します。 Dejan Milojicic: Nvidia の Tensor Core と Google の TPU を比較すると、どちらが優れていますか? Bill Dally: Google の最新の TPU についてはあまり知りませんが、Google が以前に発売した TPU はすべて専用エンジンであり、基本的には大きな乗算器と累算器のアレイが組み込まれていました。 TPU には、非線形関数やバッチノルムなどを処理するための独立したユニットがありますが、私たちのアプローチは、非常に一般的な計算ユニットをストリーミングするマルチプロセッサ (SM) を構築することであり、非常に一般的な命令だけで実行できます。何かを実行させるために使用され、その後 Tensor コアが行列乗算部分を高速化するために使用されます。つまり、Tensor Core と Google の TPU はどちらも同様の乗算器配列を持っていますが、使用する配列が比較的小さいというだけです。 デヤン・ミロジッチ: Nvidia の最大の敵は誰ですか? Bill Dally: NVIDIA は決して他社と比較しません。私たちの最大の敵は私たち自身です。私たちは常に自分自身に挑戦しています。これが正しい姿勢だと思います。」他人を盲目的に競争相手とみなすと、進歩が遅くなります。他の人がやっていることにあまり焦点を当てるのではなく、私たちは何が可能であるかに本当に焦点を当てる必要があります。私たちがやっているのは光の速度を追求するようなもので、どのように最善を尽くすか、光の速度からどれだけ離れているかにもっと注意を払うのです。これが本当の挑戦です。 デヤン・ミロジッチ: 量子コンピューティングについてどう思いますか?量子シミュレーションは深層学習の課題の自然な延長ですか? ################################## Bill Dally: 2021 年 3 月に、「cuQuantum」というソフトウェア開発キットをリリースしました。 Googleは以前にも53量子ビットを備えたコンピューターを開発し、「量子の優位性」を達成したと主張した。従来のコンピューターでは完了できない計算の一部は、cuQuantum を使用すると 5 分以内に完了できます。したがって、今日のノイズの多い中間スケール量子 (NIST) 計算ではなく、真に正確な量子アルゴリズムを実現したい場合は、GPU が最良の選択となるはずです。 Nvidia の従来の GPU コンピューターは、現在最も高速な量子コンピューターの 1 つであり、アリババも同様の古典的な計算で良好な結果を達成しており、これは私たちの結論を裏付けるものです。量子コンピューティングに対する当社の見解: Nvidia は、この技術分野のいかなる発展にも驚かないでしょう。 実は、量子コンピューティングの分野における最先端の開発を追跡する研究グループも設立しており、たとえば、IBM は 127 量子ビットのチップの開発を発表しました。また、量子ビットの数やコヒーレンス時間などの面での進歩も追跡しています。 必要な量子ビットの数、量子ビットの精度、量子上のノイズの干渉、および量子誤り訂正に必要なオーバーヘッドを考慮すると、次の 5 以内に10年も経てば量子計算は実用化できない。私の最も楽観的な見方は、約 5 年以内に人々が量子化学シミュレーションを始めるだろうということであり、それが最も可能性の高いことであるはずです。しかし、それが起こる前に、解決すべき物理的なパズルがまだたくさんあります。多くの人が気づいていないのは、量子コンピューターはアナログ コンピューターであり、アナログ コンピューターは非常に正確で簡単に分離できる必要があり、そうでないと環境との結合により一貫性のない結果が生じるということです。 デヤン・ミロジッチ: あなたの意見では、機械はいつ汎用人工知能 (AGI) のレベルに達すると思いますか? ビル・ダリー: 私はこの問題に関して否定的な考えを持っています。本質的に汎用関数フィッターであるニューラル ネットワークなど、より成功した人工知能のユースケースをいくつか見てみましょう。ニューラル ネットワークは観察を通じて機能を学習できるため、その価値は依然として人工知能ではなく人工知覚に反映されます。 これまでのところ良い結果を達成していますが、人工知能とディープラーニングを使用して生産性を向上させる方法を引き続き研究し、それによって医療と教育を改善し、より良いものを社会にもたらすことができます。人、人生。実際、これを行うために AGI は必要ありませんが、既存のテクノロジーを最大限に活用する方法に焦点を当てる必要があります。 AGI までの道のりはまだまだ長く、私たちは AGI とは何かを理解する必要もあります。 5 深層学習ハードウェアの未来

概要

以上がNVIDIA チーフ サイエンティスト: ディープ ラーニング ハードウェアの過去、現在、未来の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。