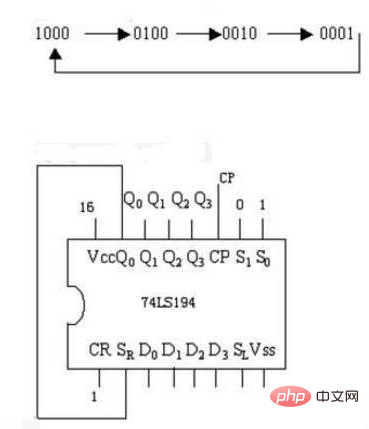

4 つのフリップフロップで構成されるリング カウンタは最大 16 状態を持ち、リング カウンタ (D0=Qn(k-1)) はシフト レジスタと特定のフィードバック回路で構成され、合計 16 状態になります。有効なカウント状態は 4 つしかなく、k 個の D フリップフロップには K 個のカウント状態がありますが、ツイスト リング カウンタの場合、リングの 2 倍である 2K 個のカウント状態があります。

拡張情報

リング カウンタは、シフト レジスタと特定のフィードバック回路で構成されており、シフト レジスタはリング カウンタの一般的なブロック図を形成するために使用されます。シフトレジスタは帰還論理回路を組み合わせた閉ループで構成され、帰還回路の出力はシフトレジスタのシリアル入力端子に接続され、帰還回路の入力端子は接続可能シフトレジスタのカウンタの種類に応じてシフトレジスタのシリアル入力端子に接続し、出力またはフリップフロップの出力を出力します。

動作原理の紹介

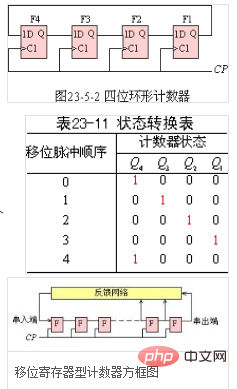

図 23-5-2 は 4 ビットのリング カウンタで、これは最も低いシフトです。レジスタ 1 ビットシリアル出力端子 Q1 を最上位シリアル入力端子 (D フリップフロップのデータ端子) にフィードバックする パルス列分配機能 (分配器) を実現するためにリングカウンタがよく使用されます。 )。レジスタの初期状態が [Q4Q3Q2Q1]=1000 であると仮定すると、シフト パルスの作用により、その状態は表 23-11 の順序で変換されます。 3 番目のシフトパルスが来ると Q1=1 となり、D4 入力端子にフィードバックされますが、4 番目のシフトパルスの作用で Q4=1 となり初期状態に戻ります。表 23-11 の各状態は、シフト パルスの作用下で 4 ビット シフト レジスタを繰り返し循環します。

FAQ列をご覧ください。

以上が4 つのフリップフロップで構成されるリング カウンタは、最大でもいくつかの有効な状態を持ちます。の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。