cache叫做高速缓冲存储器,是介于中央处理器和主存储器之间的高速小容量存储器,一般由高速SRAM构成;这种局部存储器是面向CPU的,引入它是为减小或消除CPU与内存之间的速度差异对系统性能带来的影响。Cache容量小但速度快,内存速度较低但容量大,通过优化调度算法,系统的性能会大大改善。

本教程操作环境:windows7系统、Dell G3电脑。

cache是什么存储器

Cache存储器:电脑中为高速缓冲存储器,是位于CPU和主存储器DRAM(Dynamic Random Access Memory)之间,规模较小,但速度很高的存储器,通常由SRAM(Static Random Access Memory静态存储器)组成。

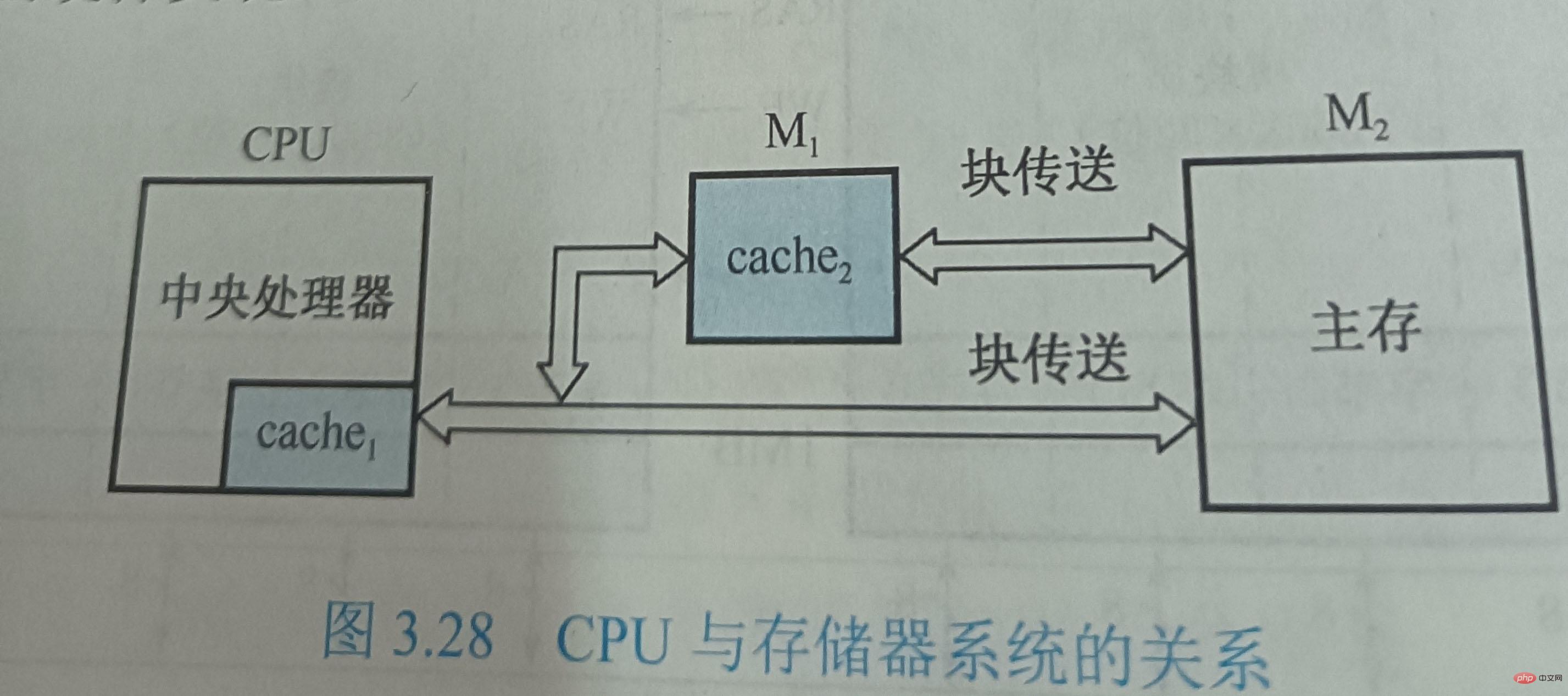

如图3.28所示,cache是介于CPU和主存M2之间的小容量存储器,但存取速度比主存快,容量远小于主存。cache 能高速地向CPU提供指令和数据,从而加快了程序的执行速度。从功能上看,它是主存的缓冲存储器,由高速的SRAM组成。为追求高速,包括管理在内的全部功能由硬件实现,因而对程序员是透明的。

当前,随着半导体器件集成度的进步提高,可以将小容量的 cache与CPU 集成到同一芯片中,其工作速度接近于CPU的速度,从而组成两级以上的cache系统。

cache的功能

Cache的功能是提高CPU数据输入输出的速率。Cache容量小但速度快,内存速度较低但容量大,通过优化调度算法,系统的性能会大大改善,仿佛其存储系统容量与内存相当而访问速度近似Cache。

CPU的速度远高于内存,当CPU直接从内存中存取数据时要等待一定时间周期,而Cache则可以保存CPU刚用过或循环使用的一部分数据,如果CPU需要再次使用该部分数据时可从Cache中直接调用,这样就避免了重复存取数据,减少了CPU的等待时间,因而提高了系统的效率。Cache又分为L1Cache(一级缓存)和L2Cache(二级缓存),L1Cache主要是集成在CPU内部,而L2Cache集成在主板上或是CPU上。

cache的基本原理

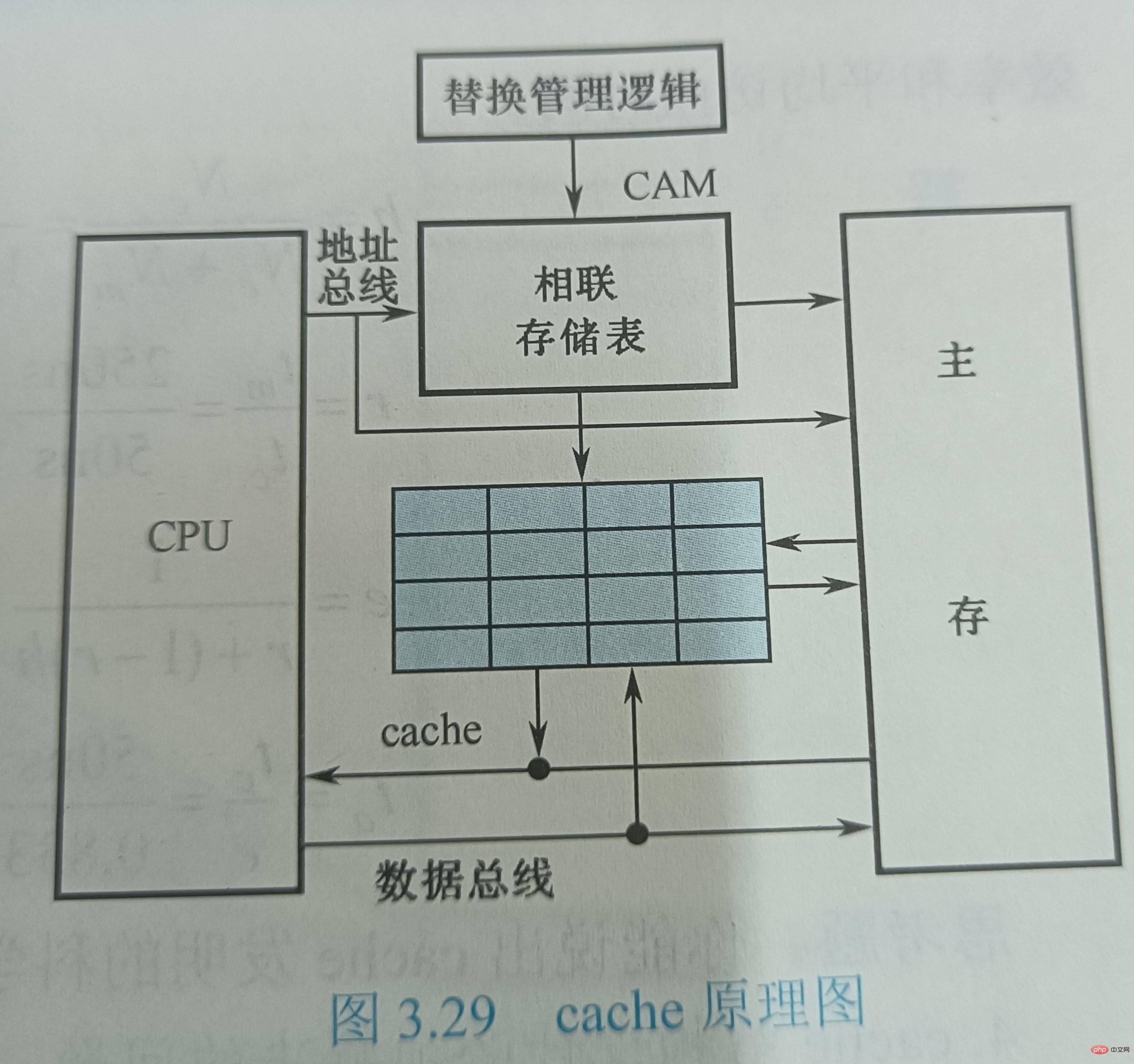

cache除包含SRAM外,还要有控制逻辑。若cache在CPU芯片外,它的控制逻辑一般与主存控制逻辑合成在一起,称为主存/chace控制器;若cache在CPU内,则由CPU提供它的控制逻辑。

CPU与cache之间的数据交换是以字为单位,而cache与主存之间的数据交换是以块为单位。一个块由若干字组成,是定长的。当CPU读取内存中一个字时,便发出此字的内存地址到cache和主存。此时cache控制逻辑依据地址判断此字当前是否在cache中:若是,则cache命中,此字立即传送给CPU;若非,则cache缺失(未命中),用主存读周期把此字从主存读出送到CPU,与此同时,把含有这个字的整个数据块从主存读出送到cache中。

图3.29示出了cache的原理图。假设cache读出时间为50ns,主存读出时间为250ns。存储系统是模块化的,主存中每个8K模块和容量16字的cache相联系。cache分为4行,每行4个字(W)。分配给cache的地址存放在一个相联存储器CAM中,它是按内容寻址的存储器。当CPU执行访存指令时,就把所要访问的字的地址送到CAM;如果W不在cache中,则将W从主存传送到CPU。与此同时,把包含W的由前后相继的4个字所组成的一行数据送入cache,替换原来cache中的一行数据。在这里,由始终管理cache使用情况的硬件逻辑电路来实现替换算法。

cache的命中率

从CPU来看,增加cache的目的,就是在性能上使主存的平均读出时间尽可能接近cache的读出时间。为了达到这个目的,在所有的存储器访问中由cache满足CPU需要的部分应占很高的比例,即cache的命中率应接近于1。由于程序访问的局部性,实现这个目标是可能的。

在一个程序执行期间,设Nc表示cache完成存取的总次数,Nₘ表示主存完成存取的总次数,h定义为命中率,则有h=Nc/(Nc+Nₘ)

若tc表示命中时的cache访问时间,tₘ表示未命中时的主存访问时间,1-h表示未命中率(缺失率),则cache/主存系统的平均访问时间tₐ为

tₐ=htc+(1−h)tₘ

我们追求的目标是,以较小的硬件代价使cache/主存系统的平均访问时间tₐ越接近 tc越好。设 r=tₘ/tc表示主存与cache的访问时间之比,e表示访问效率,则有

e=tc/ta=tc/(htc+(1−h)tm)=1/(h+(1−h)r)=1/(r+(1−r)h)

由此式看出,为提高访问效率,命中率h越接近1越好。r值以5~10为宜,不宜太大。

命中率h与程序的行为、cache的容量、组织方式、块的大小有关。

cache结构设计必须解决的问题

从cache的基本工作原理可以看出, cache的设计需要遵循两个原则:一是希望cache的命中率尽可能高,实际应接近于1;二是希望cache对CPU而言是透明的,即不论是否有cache, CPU访存的方法都是一样的,软件不需增加任何指令就可以访问cache。解决了命中率和透明性问题,就CPU访存的角度而言,内存将具有主存的容量和接近cache的速度。为此,必须增加一定的硬件电路完成控制功能,即cache控制器。

在设计cache结构时,必须解决几个问题:①主存的内容调入cache时如何存放?②访存时如何找到cache中的信息?③当cache空间不足时如何替换cache中已有的内容?④需要写操作时如何改写cache的内容?

其中,前两个问题是相互关联的,即如何将主存信息定位在cache中,如何将主存地址变换为cache地址。与主存容量相比, cache的容量很小,它保存的内容只是主存内容的一个子集,且cache与主存的数据交换是以块为单位。为了把主存块放到cache中,必须应用某种方法把主存地址定位到cache中,称为地址映射。“映射”一词的物理含义是确定位置的对应关系,并用硬件来实现。这样当CPU访问存储器时,它所给出的一个字的内存地址会自动变换成cache的地址,即cache地址变换。

cache替换问题主要是选择和执行替换算法,以便在cache不命中时替换cache中的内容。最后一个问题涉及cache的写操作策略,重点是在更新时保持主存与cache的一致性。

更多相关知识,请访问常见问题栏目!

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Une mémoire capable d'échanger des informations directement avec le CPU est une

Une mémoire capable d'échanger des informations directement avec le CPU est une

Comment implémenter un saut de ligne dans l'alerte

Comment implémenter un saut de ligne dans l'alerte

La signification de div en CSS

La signification de div en CSS

Comment créer une base de données dans MySQL

Comment créer une base de données dans MySQL

Méthode de représentation de la constante de chaîne

Méthode de représentation de la constante de chaîne

Sur quelle touche dois-je appuyer pour récupérer lorsque je ne parviens pas à taper sur le clavier de mon ordinateur ?

Sur quelle touche dois-je appuyer pour récupérer lorsque je ne parviens pas à taper sur le clavier de mon ordinateur ?

La différence entre le Wi-Fi et le Wi-Fi

La différence entre le Wi-Fi et le Wi-Fi

éditeur HTML en ligne

éditeur HTML en ligne