According to news from this website on December 27, with the explosion of AI applications, the "memory wall" has become one of the main factors restricting the performance of computing systems. CXL is built on the physical and electrical interface of PCIe. CXL memory expansion function can achieve additional memory capacity and bandwidth beyond the direct-attached DIMM slot in the server, support memory pooling and sharing, and meet the requirements of Computing power requirements of high-performance CPU/GPU.

Recently, domestic Baiwei Storage announced that it has successfully developed a CXL DRAM memory expansion module that supports the CXL 2.0 specification.

Baiwei CXL 2.0 DRAM adopts EDSFF (E3.S) form factor, memory capacity is up to 96GB, and supports PCIe 5.0×8 interface, with a theoretical bandwidth of up to 32GB/s , can be directly connected to the backplane and server motherboard that support CXL specification and E3.S interface to expand server memory capacity and bandwidth. The specification table attached to this site is as follows:

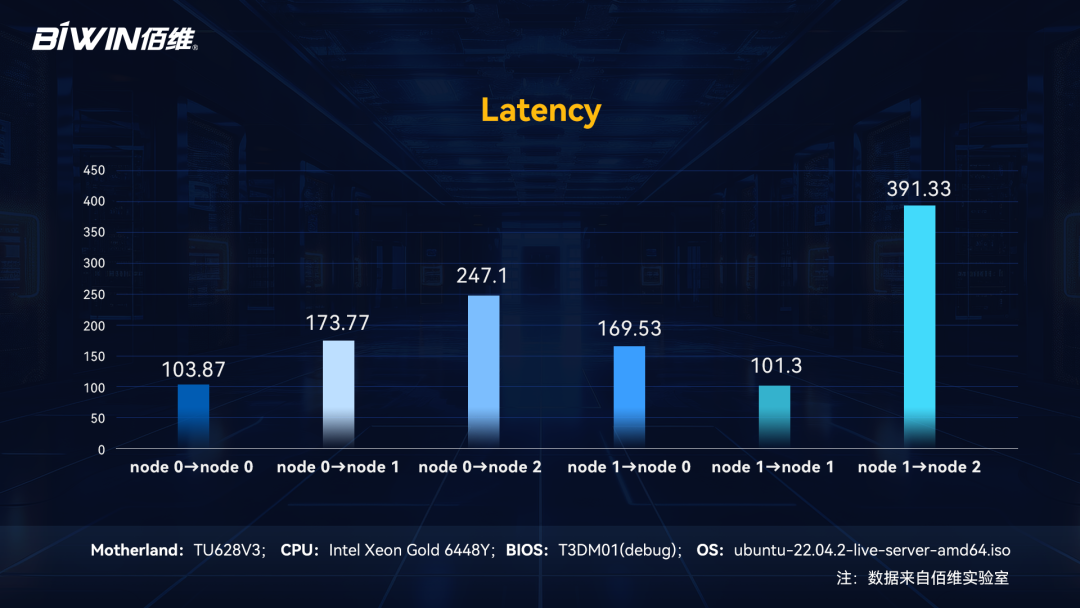

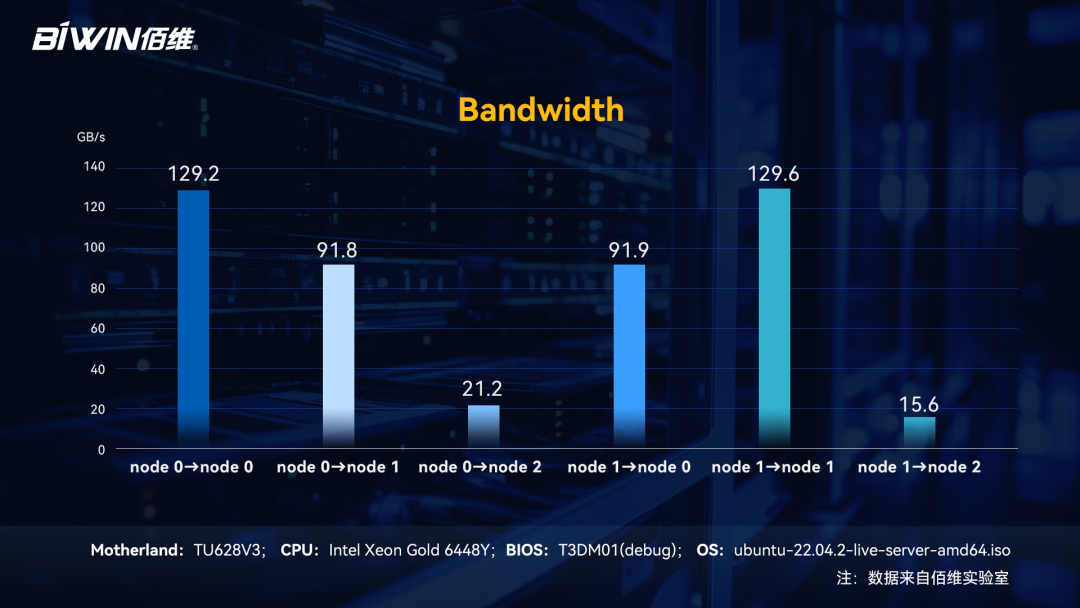

In terms of Latency performance, in the actual test, Baiwei CXL 2.0 DRAM was mounted on node 2, and mounted on The CPU access latency of node 0 is 247.1ns, and the bandwidth exceeds 21GB/s.

Baiwei representation can be used for customers and Partners provide functional prototypes of 32GB~96GB CXL 2.0 DRAM for joint evaluation and testing.

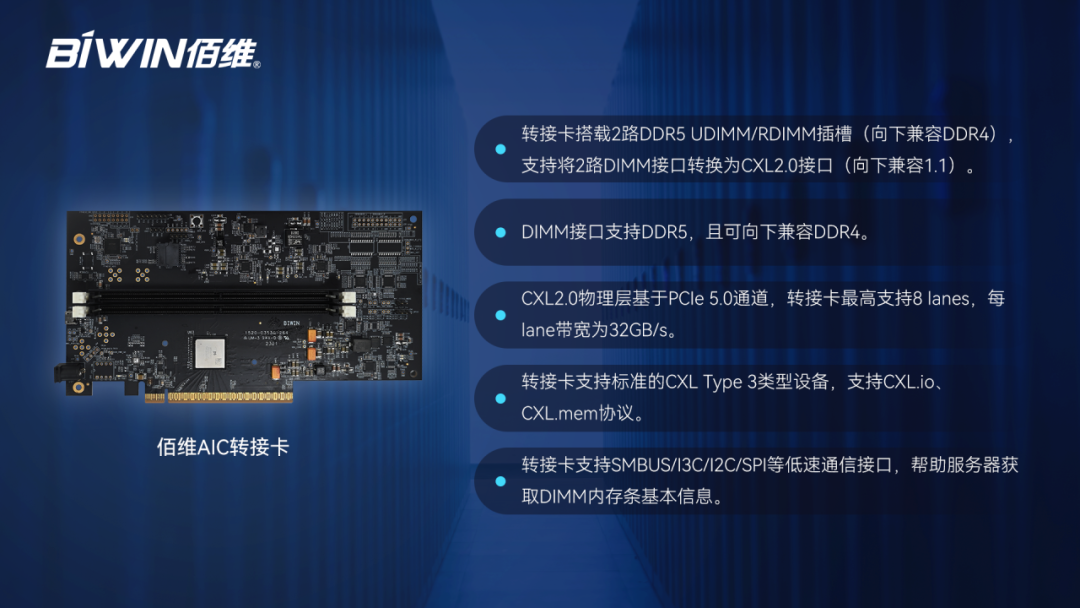

At the same time, Baiwei can provide CXL AIC adapter card for server backplane withoutE3.S interface.

The above is the detailed content of Baiwei launches domestic CXL 2.0 DRAM memory expansion module, which can reach a maximum capacity of 96GB and a theoretical bandwidth of 32GB/s. For more information, please follow other related articles on the PHP Chinese website!

How to check memory

How to check memory

What are the video server configuration parameters?

What are the video server configuration parameters?

How to solve too many logins

How to solve too many logins

windows cannot open add printer

windows cannot open add printer

what is c#

what is c#

Solution to the problem that setting the Chinese interface of vscode does not take effect

Solution to the problem that setting the Chinese interface of vscode does not take effect

How to cut long pictures on Huawei mobile phones

How to cut long pictures on Huawei mobile phones

How to format hard drive in linux

How to format hard drive in linux